# SLC 500<sup>™</sup> Instruction Set

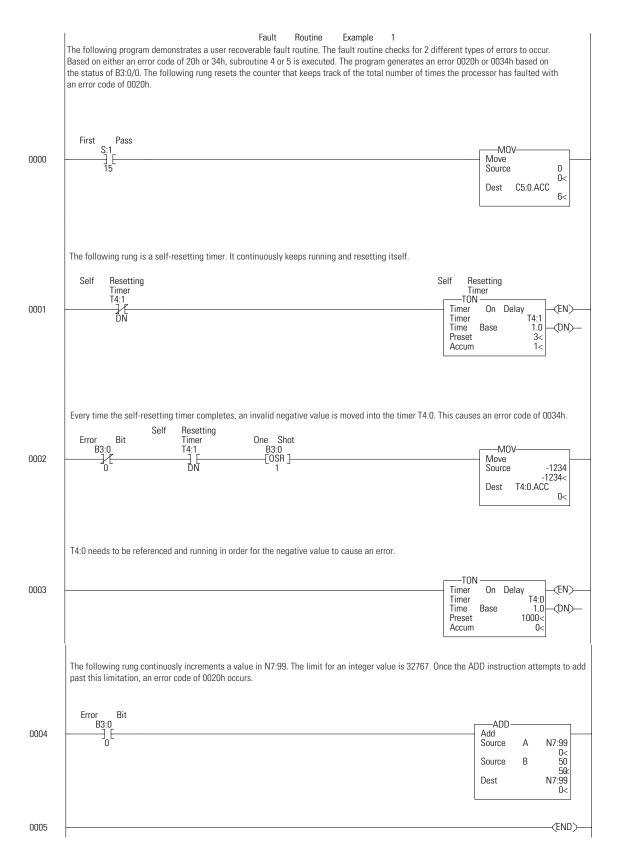

Catalog Numbers 1747-L20x, 1747-L30x, 1747-L40x, 1747-L511, 1747-L514, 1747-L524, 1747-L531, 1747-L532, 1747-L541, 1747-L542, 1747-L543, 1747-L551, 1747-L552, 1747-L553

**Reference Manual**

# **Important User Information** Because of the variety of uses for the products described in this publication, those responsible for the application and use of this control equipment must satisfy themselves that all necessary steps have been taken to assure that each application and use meets all performance and safety requirements, including any applicable laws, regulations, codes and standards.

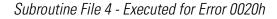

The illustrations, charts, sample programs and layout examples shown in this guide are intended solely for purposes of example. Since there are many variables and requirements associated with any particular installation, Allen-Bradley does not assume responsibility or liability (to include intellectual property liability) for actual use based upon the examples shown in this publication.

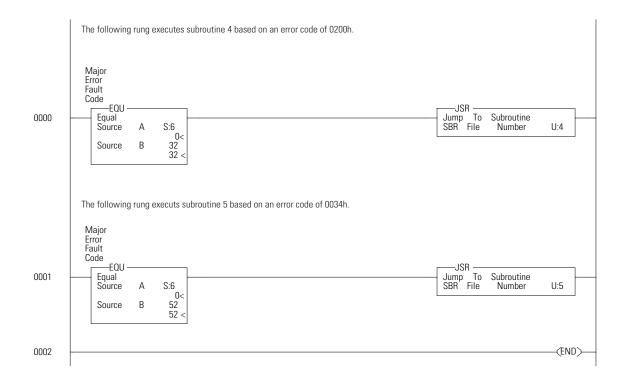

Allen-Bradley publication SGI-1.1, *Safety Guidelines for the Application, Installation and Maintenance of Solid-State Control* (available from your local Allen-Bradley office), describes some important differences between solid-state equipment and electromechanical devices that should be taken into consideration when applying products such as those described in this publication.

Reproduction of the contents of this copyrighted publication, in whole or part, without written permission of Rockwell Automation, is prohibited.

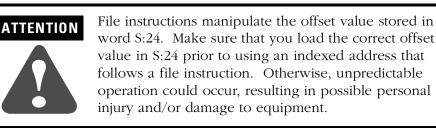

Throughout this manual we use notes to make you aware of safety considerations:

Identifies information about practices or circumstances that can lead to personal injury or death, property damage or economic loss

Attention statements help you to:

- identify a hazard

- avoid a hazard

- recognize the consequences

IMPORTANT

Identifies information that is critical for successful application and understanding of the product.

PLC-2, PLC-3, and PLC-5 are registered trademarks of Rockwell Automation. SLC 500, SLC 5/01, SLC 5/02, SLC 5/04, SLC 5/05 and Data Highway Plus are trademarks of Rockwell Automation. WINtelligent EMULATE 500, WINtelligent LINX, RSLogix 500, RSLinx, and RSTune are trademarks of Rockwell Software, Inc. Ethernet is a registered trademark of Digital Equipment Corporation, Intel, and Xerox Corporation. MS-DOS and Windows 95 are registered trademarks and Windows NT is a trademark of Microsoft Corporation. NEC Versa is a trademark of Dippon Electric Company Information Systems, Inc. Gateway 2000 is a trademark of Gatemway 2000, Inc. The information below summarizes the changes to this manual since the last printing.

To help you find new and updated information in this release of the manual, we have included change bars as shown next to this paragraph.

The table below lists the sections that document new features and additional or updated information about existing features.

| For this information                                                                                                                                                                                                                               | See               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Removed references to MicroLogix 1000.                                                                                                                                                                                                             | Throughout        |

| Created section explaining Data Files and Program Files                                                                                                                                                                                            | Chapter 1         |

| Removed Processor Files information. Revisions to the Basic Instructions.                                                                                                                                                                          | Chapter 2         |

| Revisions to the Comparison Instructions.                                                                                                                                                                                                          | Chapter 3         |

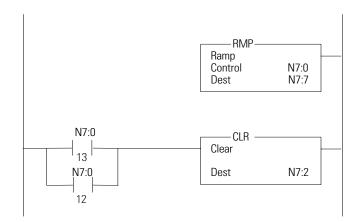

| Revisions to the Math Instructions. Added Ramp Instruction (RMP).                                                                                                                                                                                  | Chapter 4         |

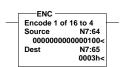

| Revisions to the Data Handling Instructins. Added Encode 1 to 16 to 4 Instruction (ENC).                                                                                                                                                           | Chapter 5         |

| Revisions to the Program Flow Instructions                                                                                                                                                                                                         | Chapter 6         |

| Revisions to the Application Specific Instructions. Added the following instructions: Read High-Speed Clock<br>Instruction (RHC), Compute Time Difference Instruction (TDF), File Bit Comparison Instruction (FBC) and Diagnostic<br>Detect (DDT). | Chapter 7         |

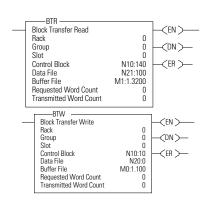

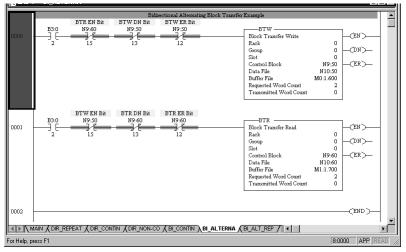

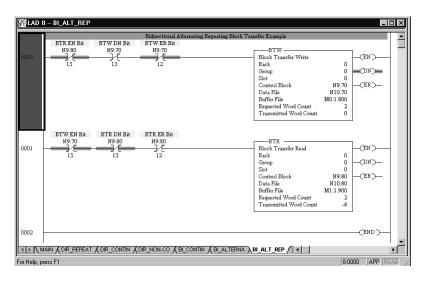

| Added Remote I/O Block Transfer Instructions (BTR and BTW).                                                                                                                                                                                        | Chapter 8         |

| Revisions to the PID Instruction.                                                                                                                                                                                                                  | Chapter 9         |

| Revisions to the ASCII Instructions.                                                                                                                                                                                                               | Chapter 10        |

| Revisions to the Interrupt Routines.                                                                                                                                                                                                               | Chapter 11        |

| Revisions to the Communication Instructions.                                                                                                                                                                                                       | Chapter 12        |

| Created section for Communication Channels.                                                                                                                                                                                                        | Chapter 13        |

| Created section for Messaging Examples.                                                                                                                                                                                                            | Chapter 14        |

| Revisions to the Troubleshooting section.                                                                                                                                                                                                          | Chapter 15        |

| Removed execution times, combined the memory usage tables for SLC 5/03, SLC 5/04 and SLC 5/05. Added memory usage for new instructions.                                                                                                            | Appendix C        |

| Removed the estimating scan time section. Added new instructions to the Programming Instruction References section.                                                                                                                                | Appendix D        |

| Updated ladder diagrams for the application examples.                                                                                                                                                                                              | Appendix G        |

| Alphabetical list of all instructions.                                                                                                                                                                                                             | Inside Back Cover |

Summary of Changes 2

| Preface                 | Who Should Use this Manual.1Purpose of this Manual1Common Techniques Used in this Manual1Rockwell Automation Support2Related Documentation3 |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Chapter 1                                                                                                                                   |

| Processor Files         | File Structure    1-1                                                                                                                       |

|                         | Chapter 2                                                                                                                                   |

| Basic Instructions      | About the Basic Instructions2-2Bit Instructions Overview2-2Examine if Closed (XIC)2-3                                                       |

|                         | Examine if Open (XIO)                                                                                                                       |

|                         | Output Energize (OTE)2-4Output Latch (OTL) and Output Unlatch (OTU)2-4                                                                      |

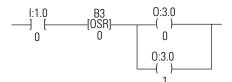

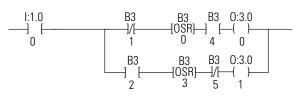

|                         | One-Shot Rising (OSR)                                                                                                                       |

|                         | Timer Instructions Overview                                                                                                                 |

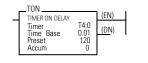

|                         | Timer On-Delay (TON)2-9                                                                                                                     |

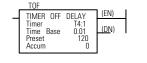

|                         | Timer Off-Delay (TOF)                                                                                                                       |

|                         | Retentive Timer (RTO)2-11Counter Instructions Overview2-13                                                                                  |

|                         | Count Up (CTU)                                                                                                                              |

|                         | Count Down (CTD)                                                                                                                            |

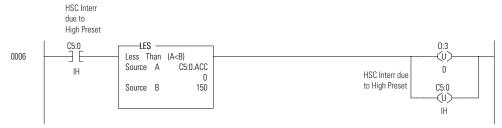

|                         | High-Speed Counter (HSC) 2-15                                                                                                               |

|                         | Reset (RES)                                                                                                                                 |

|                         | Chapter 3                                                                                                                                   |

| Comparison Instructions | About the Comparison Instructions                                                                                                           |

| -                       | Comparison Instructions Overview                                                                                                            |

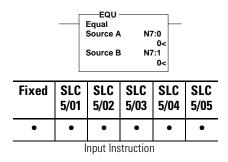

|                         | Equal (EQU)                                                                                                                                 |

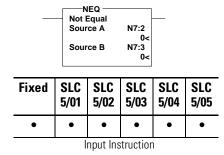

|                         | Not Equal (NEQ).         3-2           Loss Then (LES)         3-2                                                                          |

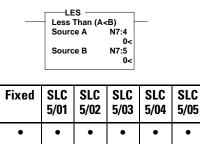

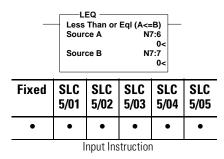

|                         | Less Than (LES)3-3Less Than or Equal (LEQ)3-3                                                                                               |

|                         | Greater Than (GRT)                                                                                                                          |

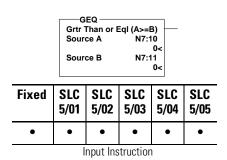

|                         | Greater Than or Equal (GEQ)                                                                                                                 |

|                         | Masked Comparison for Equal (MEQ) 3-4                                                                                                       |

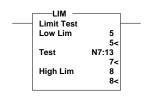

|                         | Limit Test (LIM) 3-4                                                                                                                        |

|                         | Chapter 4                                                                                                                                   |

| Math Instructions       | About the Math Instructions                                                                                                                 |

|                         | Math Instructions Overview 4-2                                                                                                              |

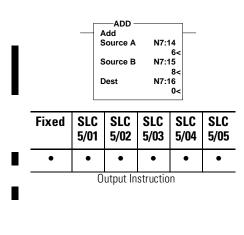

|                         | Add (ADD) 4-5                                                                                                                               |

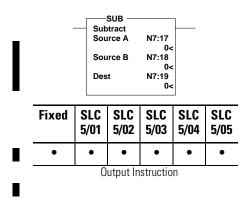

|                         | Subtract (SUB) 4-5                                                                                                                          |

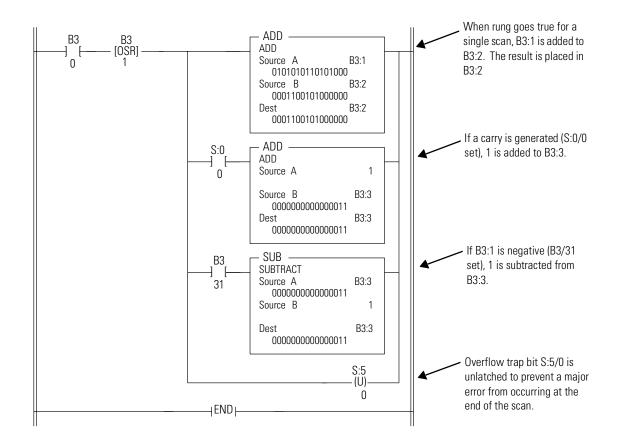

|                         | 32-Bit Addition and Subtraction                                                                                                             |

| Multiply (MUL)                   |

|----------------------------------|

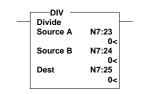

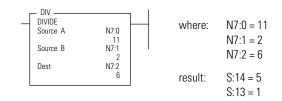

| Divide (DIV)                     |

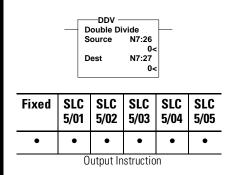

| Double Divide (DDV)              |

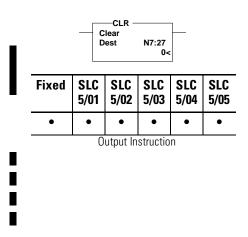

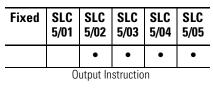

| Clear (CLR)                      |

| Square Root (SQR)                |

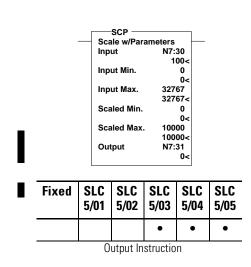

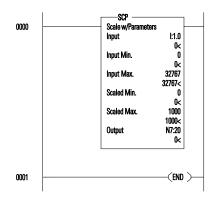

| Scale with Parameters (SCP) 4-13 |

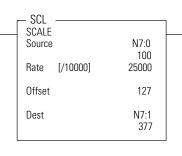

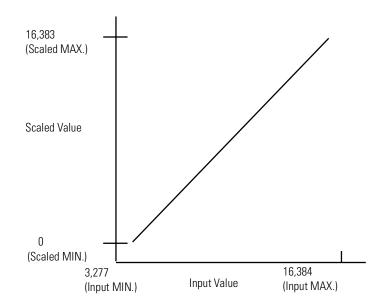

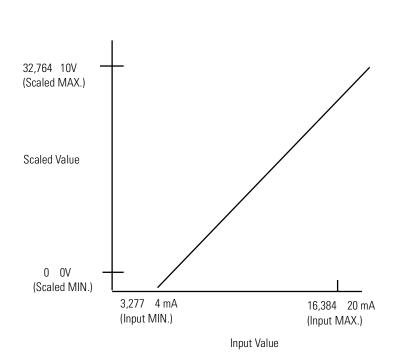

| Scale Data (SCL)                 |

| Ramp Instruction (RMP) 4-20      |

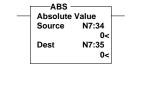

| Absolute (ABS)                   |

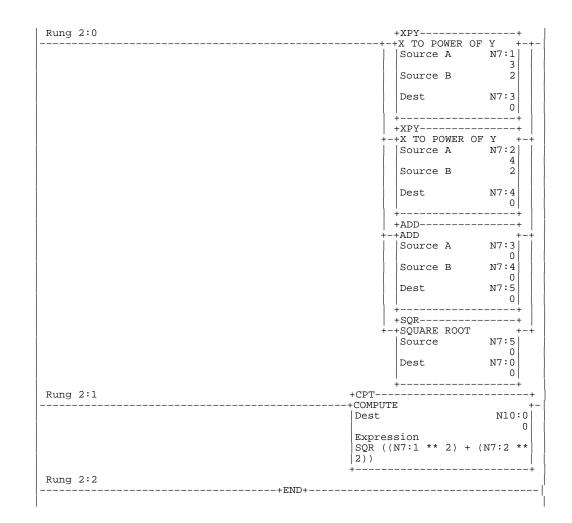

| Compute (CPT)                    |

| Swap (SWP)                       |

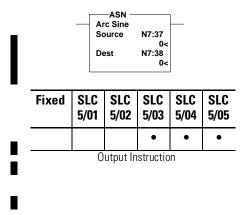

| Arc Sine (ASN)                   |

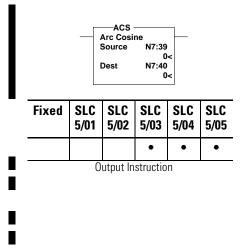

| Arc Cosine (ACS)                 |

| Arc Tangent (ATN)                |

| Cosine (COS)                     |

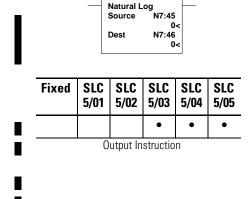

| Natural Log (LN)                 |

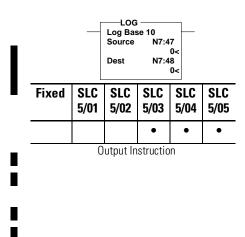

| Log to the Base 10 (LOG)         |

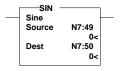

| Sine (SIN)                       |

| Tangent (TAN)                    |

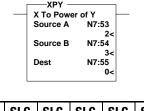

| X to the Power of Y (XPY) 4-32   |

|                                  |

## **Chapter 5**

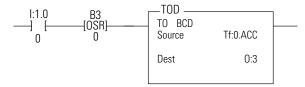

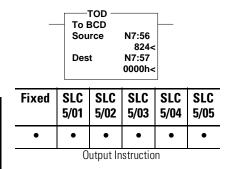

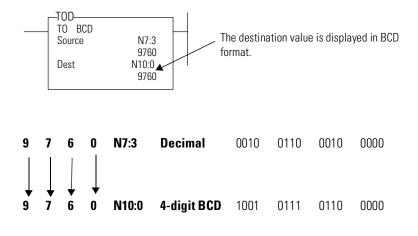

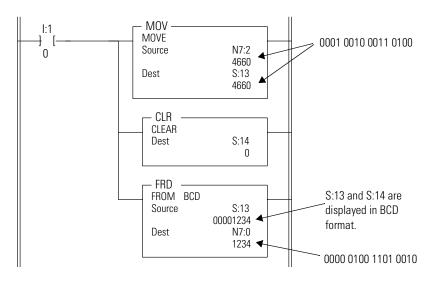

| Convert to BCD (TOD) 5-2                              |

|-------------------------------------------------------|

| Convert from BCD (FRD)                                |

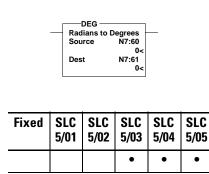

| Radian to Degrees (DEG)5-8                            |

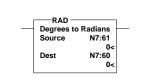

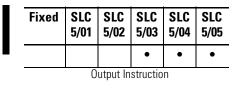

| Degrees to Radians (RAD)                              |

|                                                       |

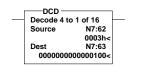

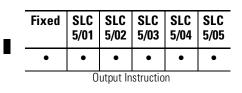

| Decode 4 to 1 of 16 (DCD)                             |

| Encode 1 of 16 to 4 (ENC)                             |

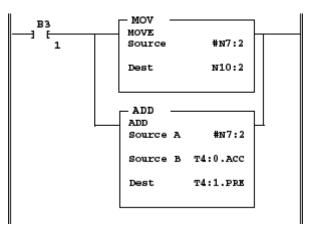

| Copy File (COP) and Fill File (FLL) Instructions 5-12 |

| Move and Logical Instructions Overview                |

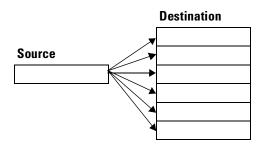

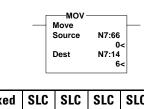

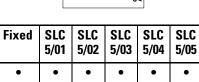

| Move (MOV)                                            |

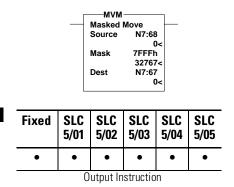

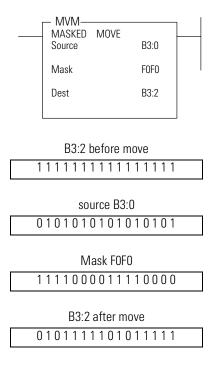

| Masked Move (MVM)                                     |

| And (AND)                                             |

| Or (OR)                                               |

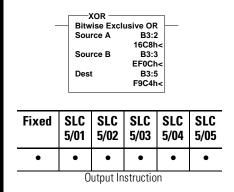

| Exclusive Or (XOR)                                    |

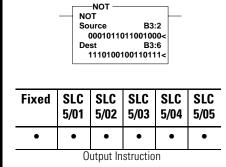

| Not (NOT)                                             |

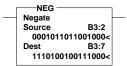

| Negate (NEG)                                          |

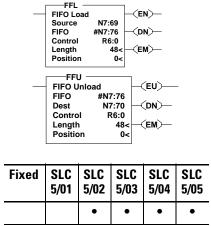

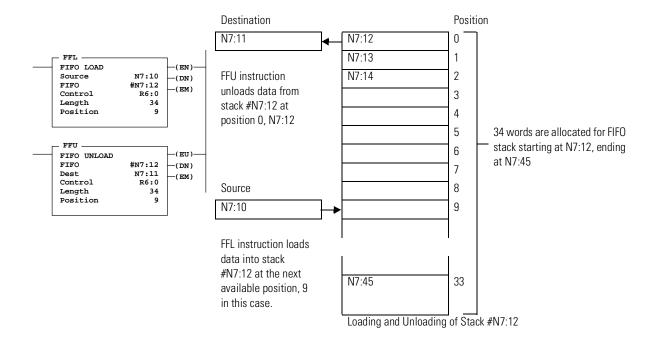

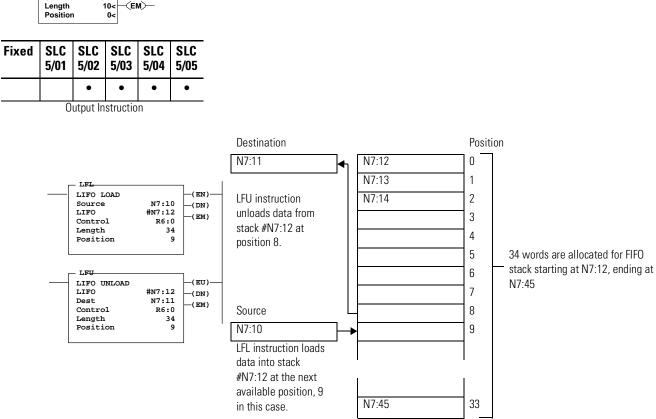

| FIFO and LIFO Instructions Overview                   |

| FIFO Load (FFL) and FIFO Unload (FFU)5-26             |

| LIFO Load (LFL) and LIFO Unload (LFU)                 |

**Data Handling Instructions**

|                                   | Chapter 6                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

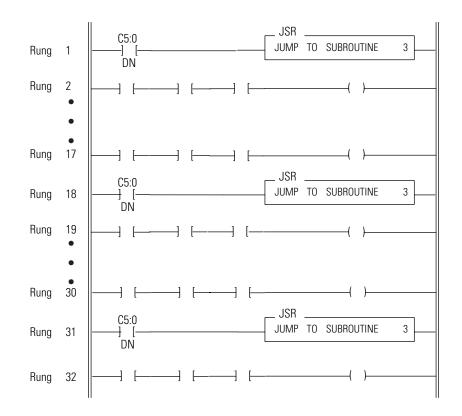

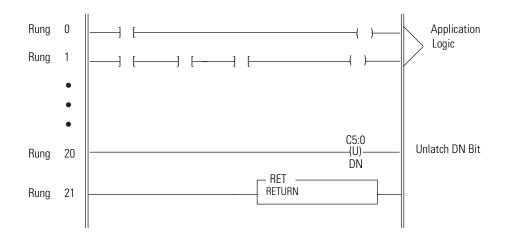

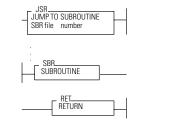

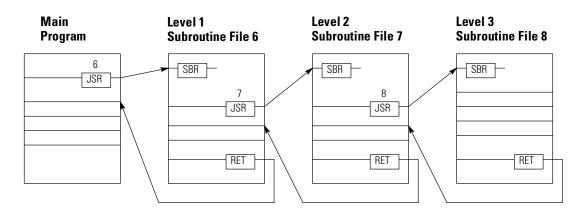

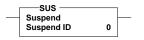

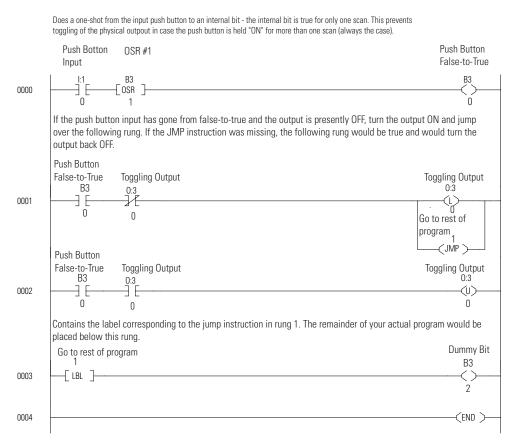

| Program Flow Instructions         | About the Program Flow Control Instructions.6-1Jump (JMP) and Label (LBL)6-2Jump to Subroutine (JSR),Subroutine (SBR), and Return (RET).6-3Master Control Reset (MCR).6-6                                                                                                                                                                                                                                                                                    |

|                                   | Temporary End (TND)6-7                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                   | Suspend (SUS)                                                                                                                                                                                                                                                                                                                                                                                                                                                |

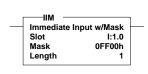

|                                   | Immediate Input with Mask (IIM)                                                                                                                                                                                                                                                                                                                                                                                                                              |

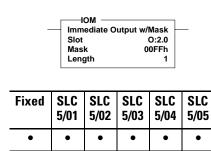

|                                   | Immediate Output with Mask (IOM)6-9I/O Refresh (REF)6-10                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                   | Chapter 7                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

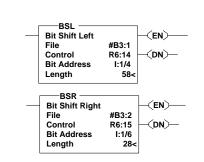

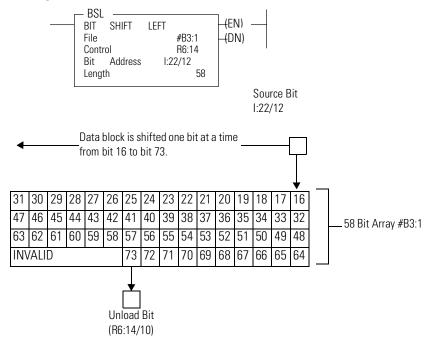

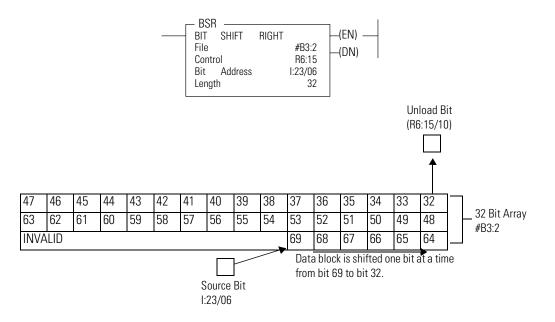

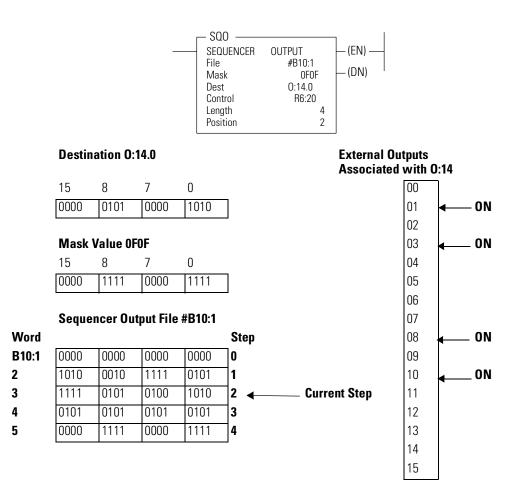

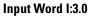

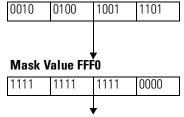

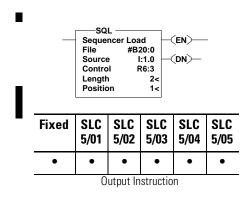

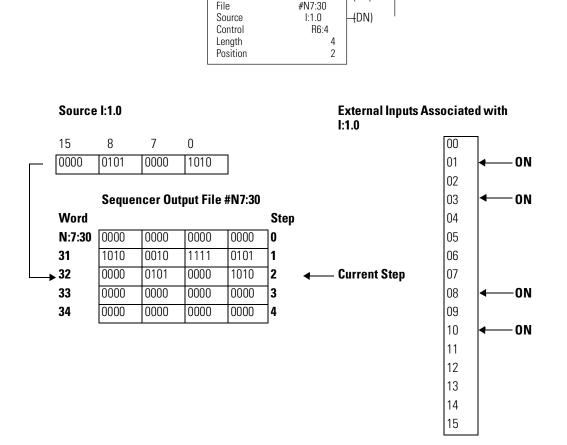

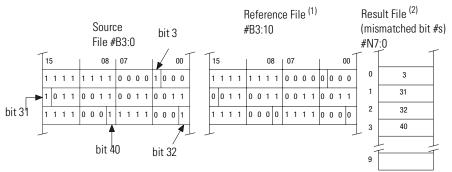

| Application Specific Instructions | About the Application Specific Instructions7-2Bit Shift Instructions Overview.7-2Bit Shift Left (BSL) Bit Shift Right (BSR)7-4Sequencer Instructions Overview.7-5Sequencer Output (SQO) Sequencer Compare (SQC)7-6Sequencer Load (SQL)7-12Read High-Speed Clock and7-15Compute Time Difference Overview7-15Read High-Speed Clock Instruction (RHC)7-17Compute Time Difference Instruction (TDF)7-17File Bit Comparison (FBC) and Diagnostic Detect (DDT)7-18 |

|                                   | Chapter 8                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Block Transfer Instructions       | Block Transfer Instructions (BTR and BTW) 8-1                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   | Chapter 9                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

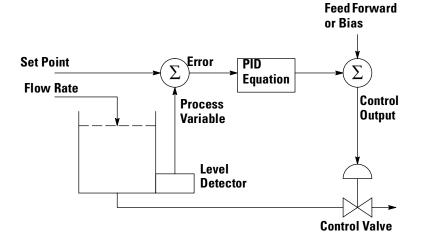

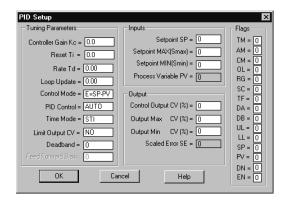

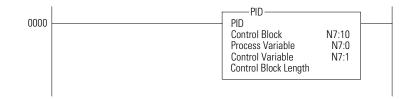

| Proportional Integral Derivative  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Instruction                       | The PID Concept                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                   | The PID Equation                                                                                                                                                                                                                                                                                                                                                                                                                                             |

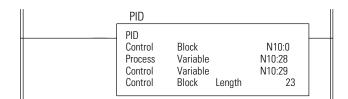

|                                   | The PID Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                   | PID Control Block Layout                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                   | Input Parameters9-14Output Parameters9-16                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                   | Runtime Errors                                                                                                                                                                                                                                                                                                                                                                                                                                               |

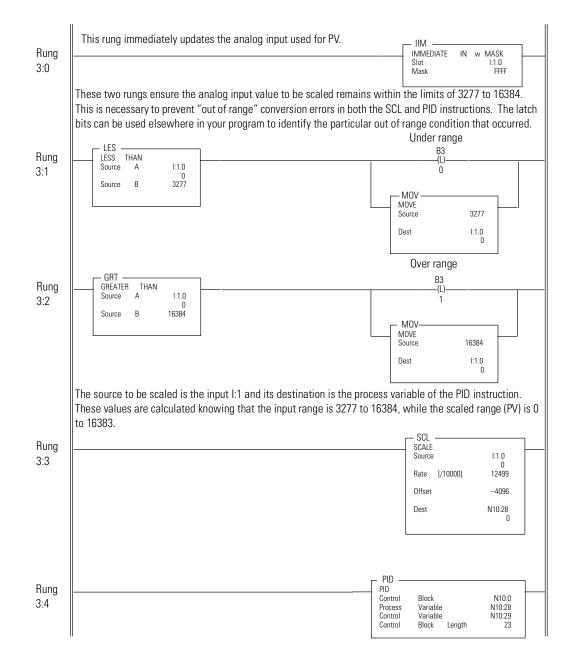

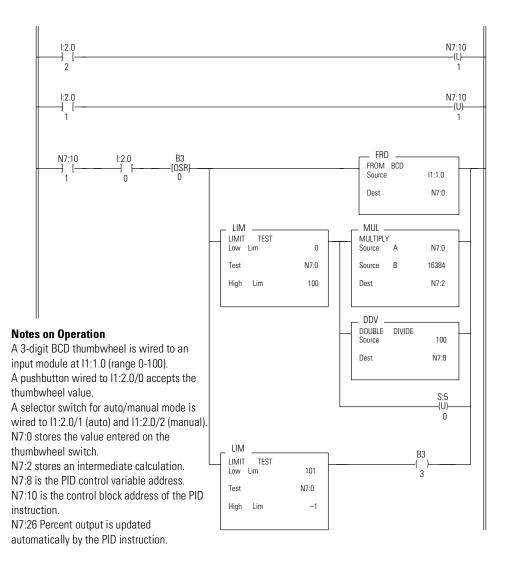

|                                   | PID and Analog I/O Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                   | Application Notes                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## **ASCII Instructions**

## Chapter 10

| ASCII Instruction Overview                        |

|---------------------------------------------------|

| Protocol Parameter Overview                       |

| Test Buffer for Line (ABL)                        |

| Number of Characters In Buffer (ACB) 10-7         |

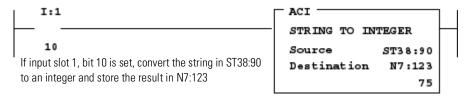

| String to Integer (ACI)                           |

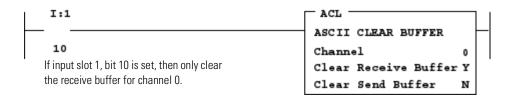

| ASCII Clear Receive and/or Send Buffer (ACL) 10-9 |

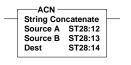

| String Concatenate (ACN) 10-10                    |

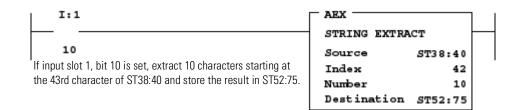

| String Extract (AEX) 10-10                        |

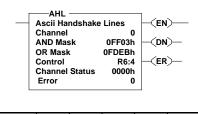

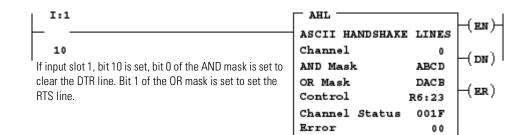

| ASCII Handshake Lines (AHL)                       |

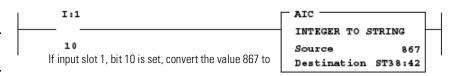

| Integer to String (AIC) 10-13                     |

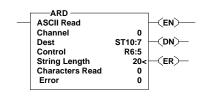

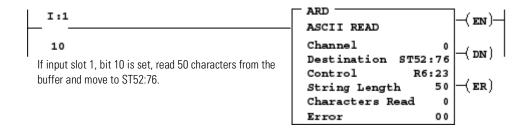

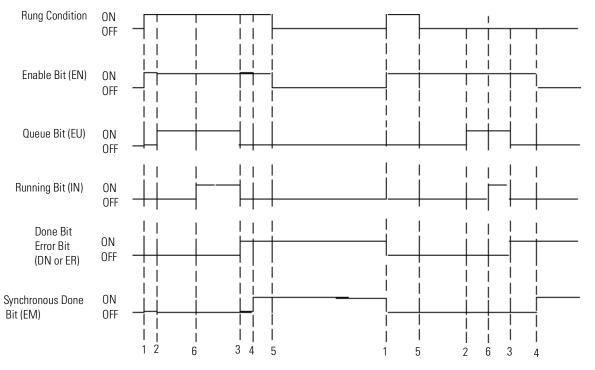

| ASCII Read Characters (ARD)                       |

| ASCII Read Line (ARL)                             |

| String Search (ASC) 10-17                         |

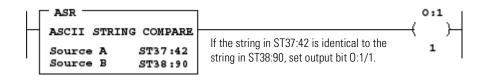

| ASCII String Compare (ASR) 10-18                  |

| ASCII Write with Append (AWA) 10-19               |

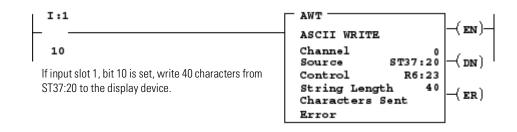

| ASCII Write (AWT) 10-21                           |

| ASCII Instruction Error Codes 10-23               |

| ASCII Conversion Table                            |

## Chapter 11

|                                  | -                                   |

|----------------------------------|-------------------------------------|

| Understanding Interrupt Routines | User Fault Routine Overview         |

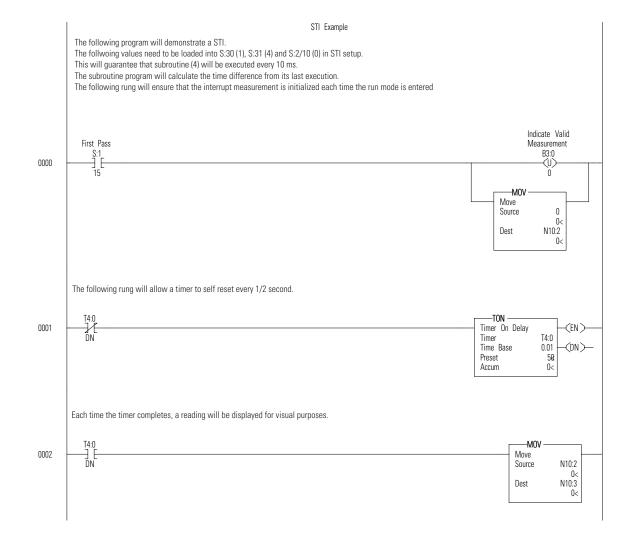

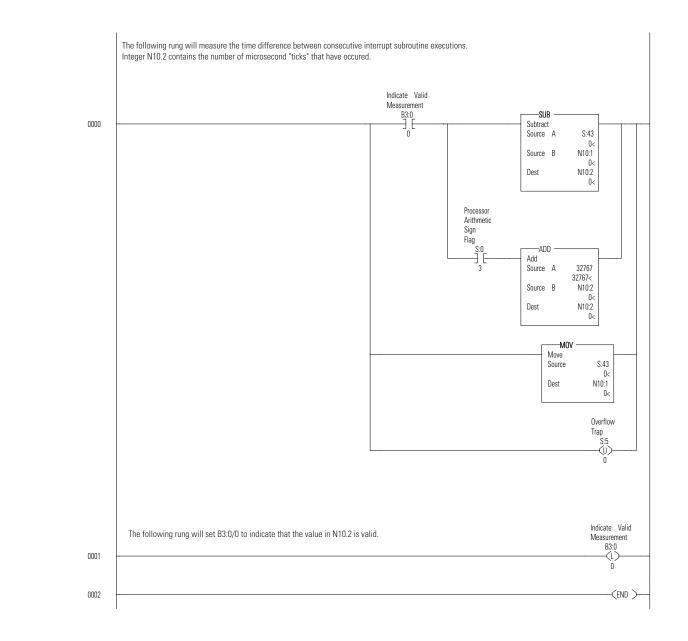

|                                  | Selectable Timed Interrupt Overview |

|                                  | Operation                           |

|                                  | STI Parameters 11-13                |

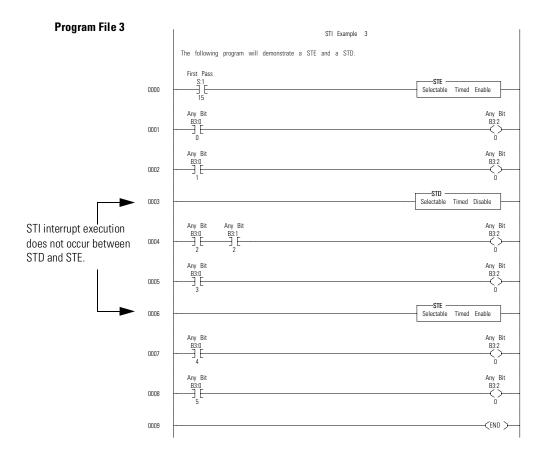

|                                  | STD and STE Instructions 11-17      |

|                                  | Selectable Timed Start (STS) 11-18  |

|                                  | Discrete Input Interrupt Overview   |

|                                  | Operation                           |

|                                  | DII Parameters 11-24                |

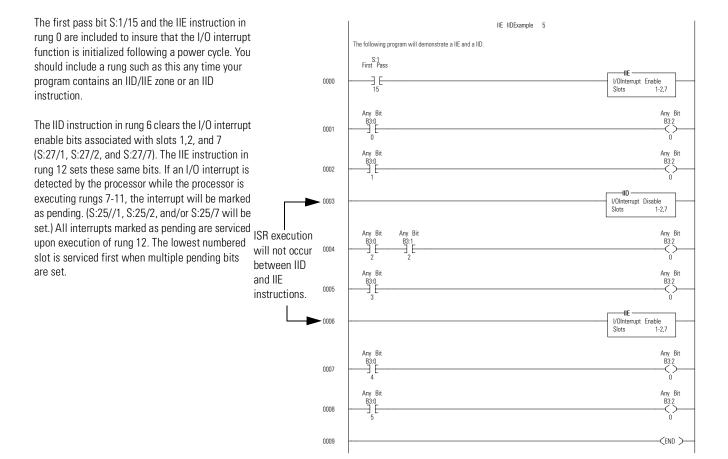

|                                  | I/O Interrupt Overview              |

|                                  | Operation                           |

|                                  | I/O Interrupt Parameters            |

|                                  | I/O Interrupt Disable (IID) and     |

|                                  | I/O Interrupt Enable (IIE) 11-34    |

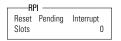

|                                  | Reset Pending Interrupt (RPI) 11-36 |

|                                  | Interrupt Subroutine (INT)          |

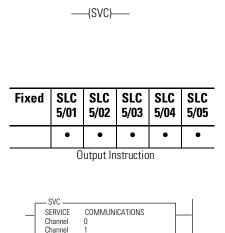

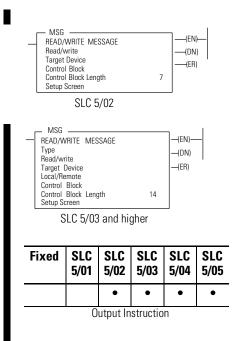

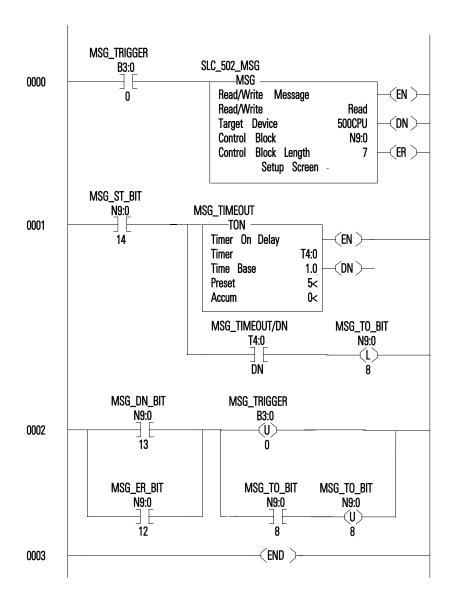

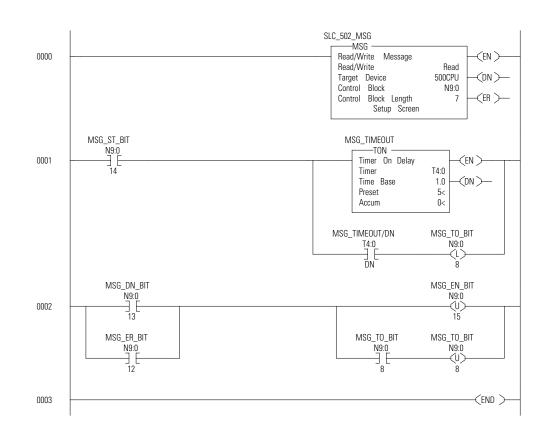

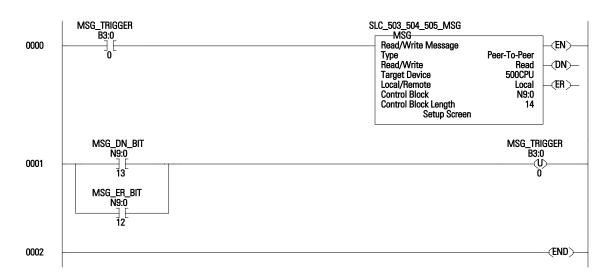

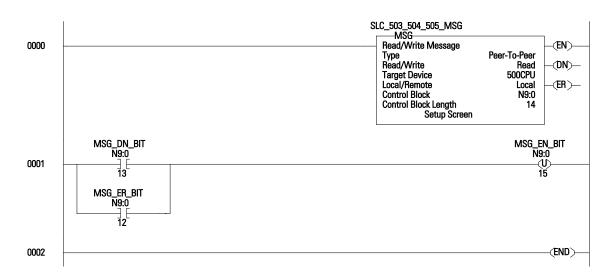

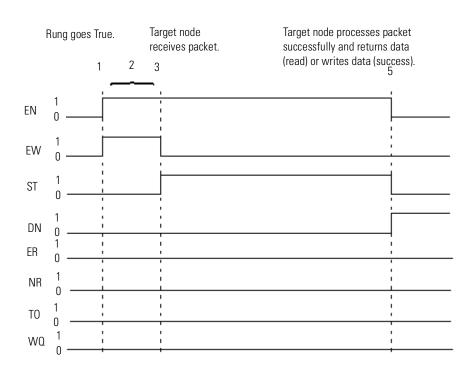

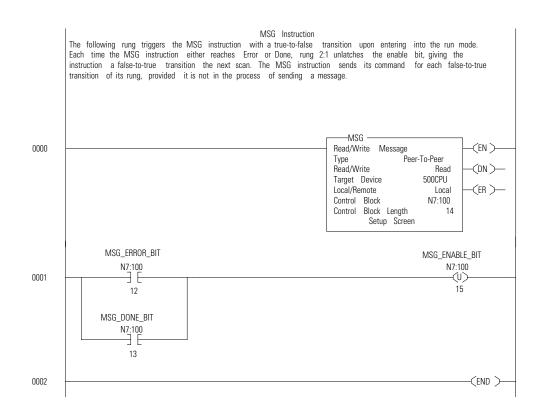

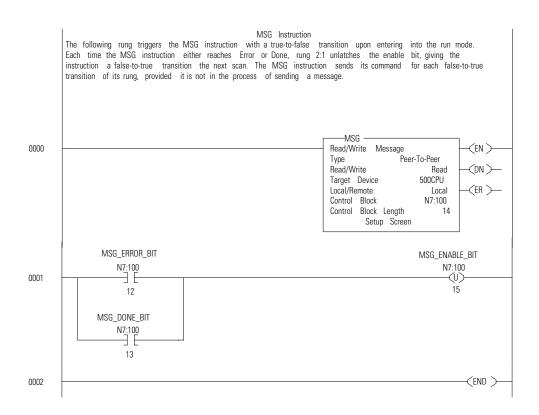

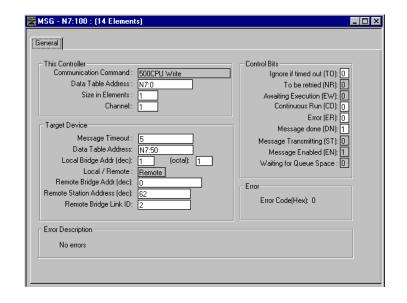

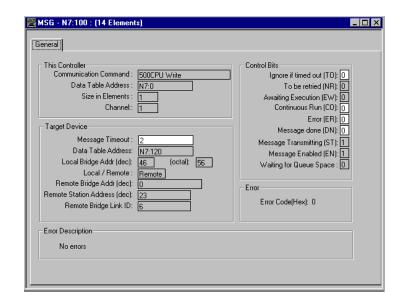

| SLC Communication Instructions | About the Communication Instructions12-1Service Communications (SVC)12-2Message Instruction Overview12-3Timing Diagram for SLC 5/03, SLC 5/04, and12-25SLC 5/05 MSG Instruction12-25MSG Instruction Error Codes12-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | Chapter 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

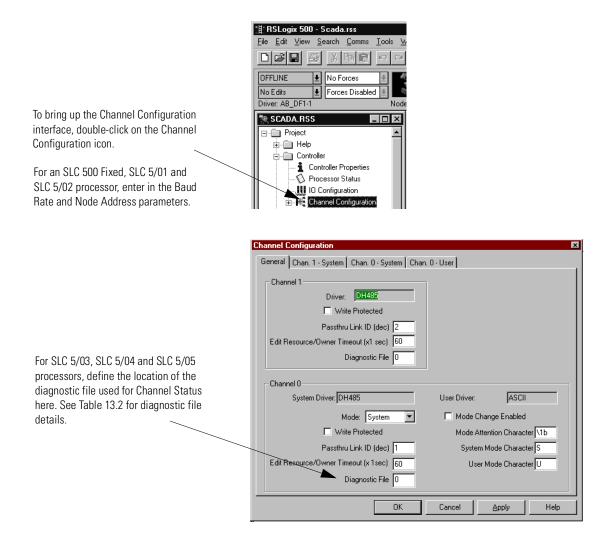

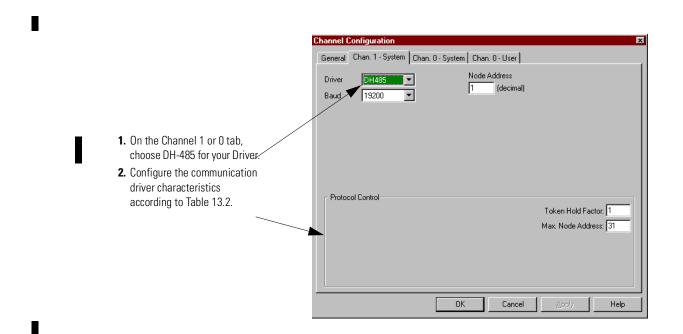

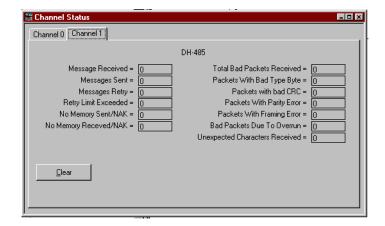

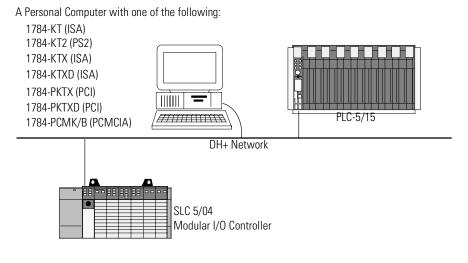

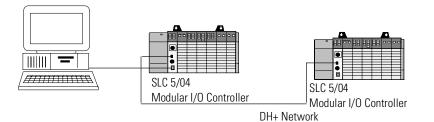

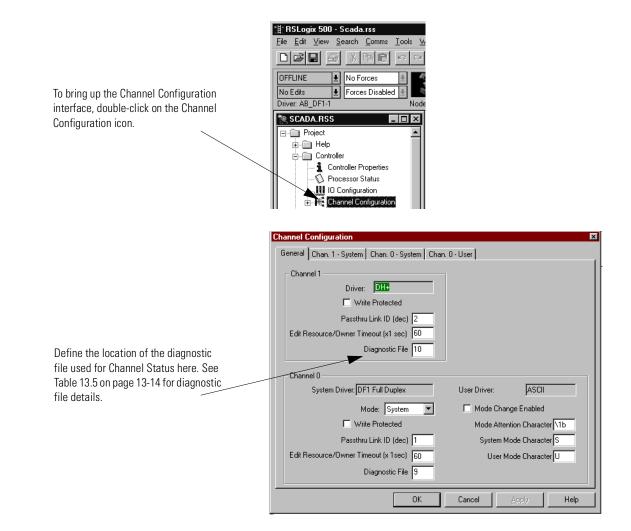

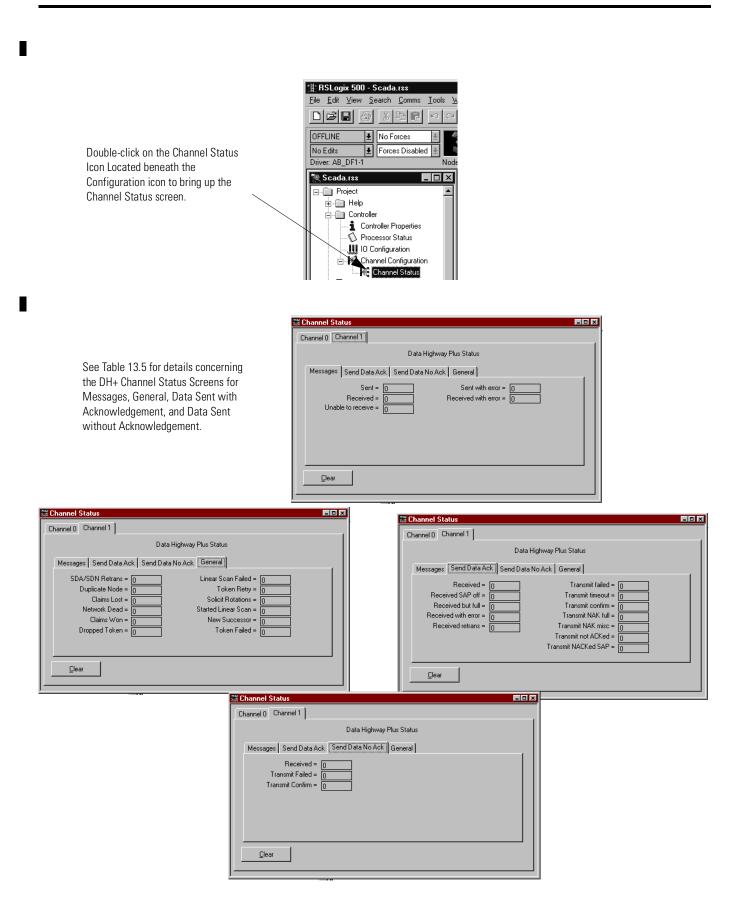

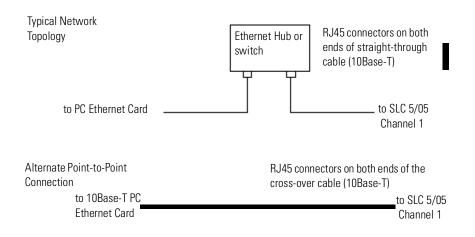

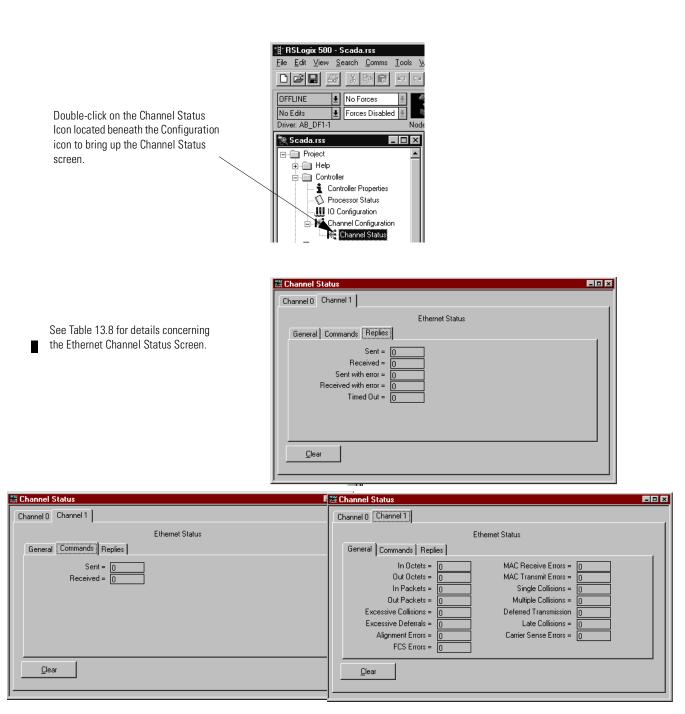

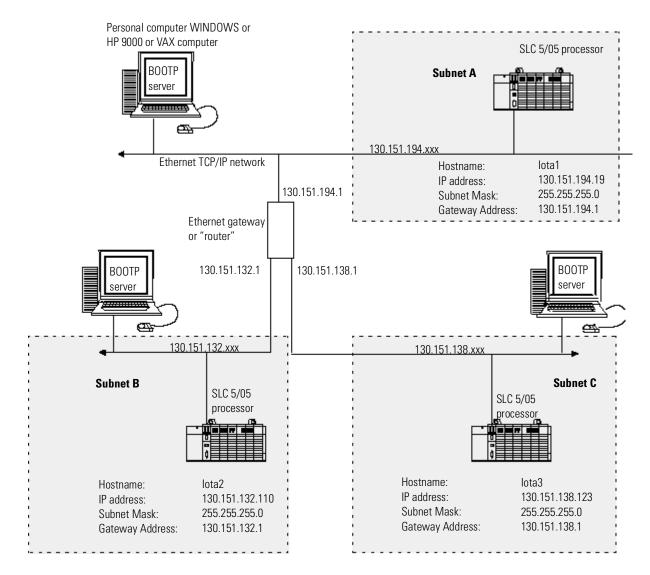

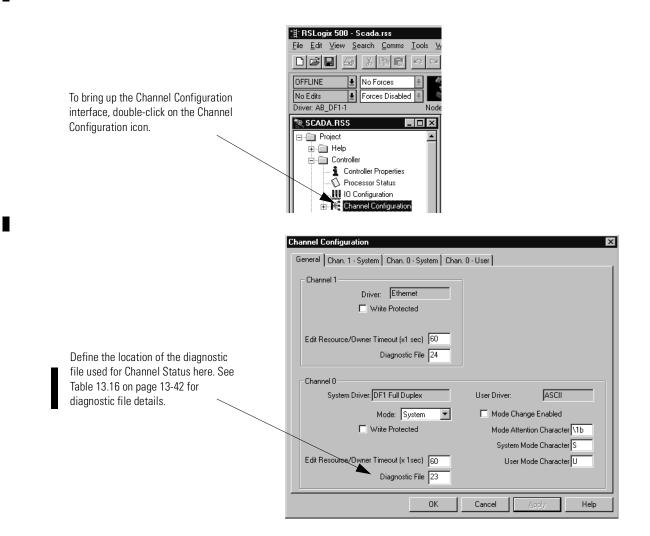

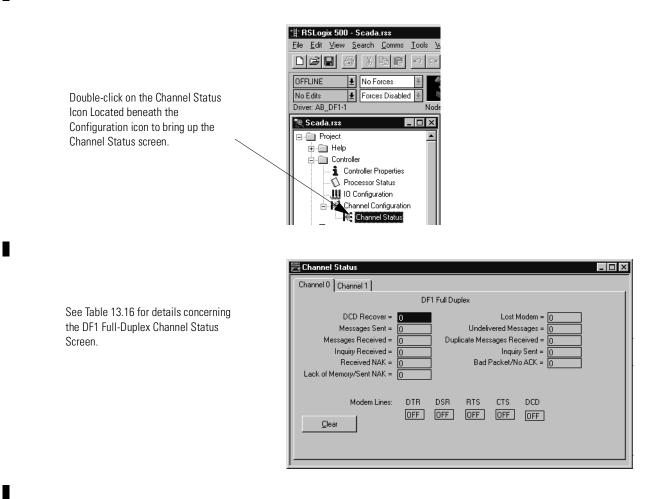

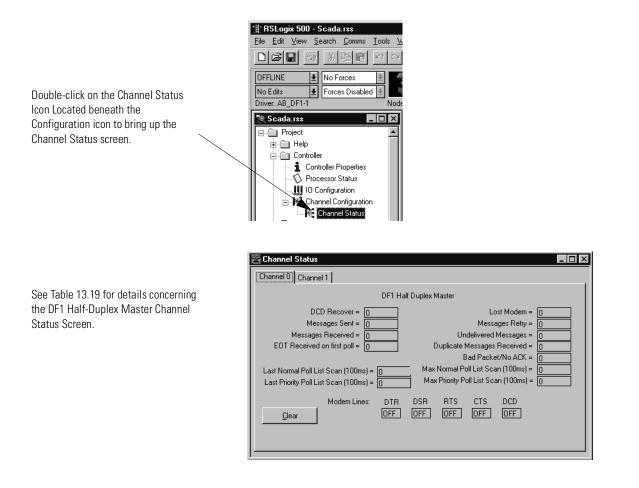

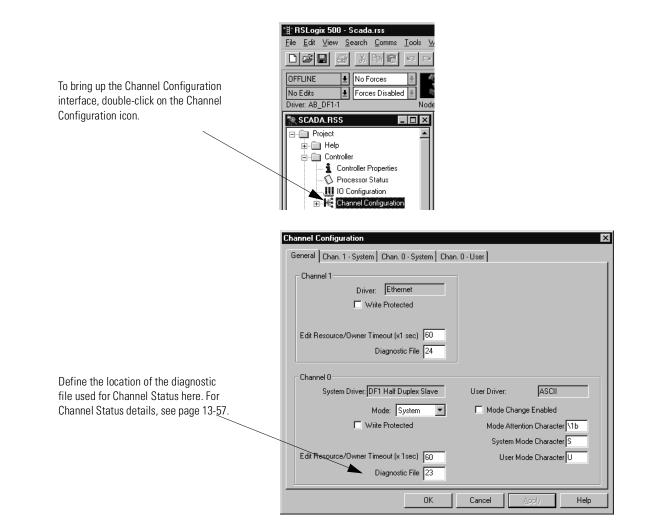

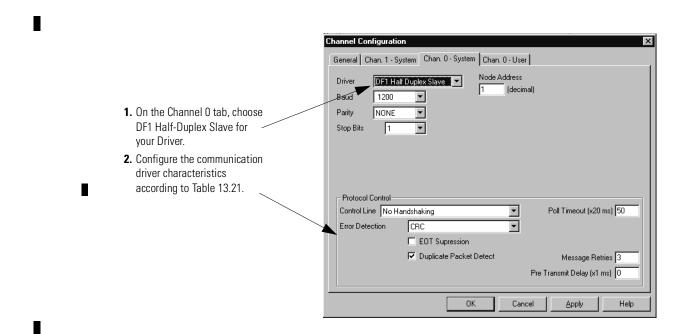

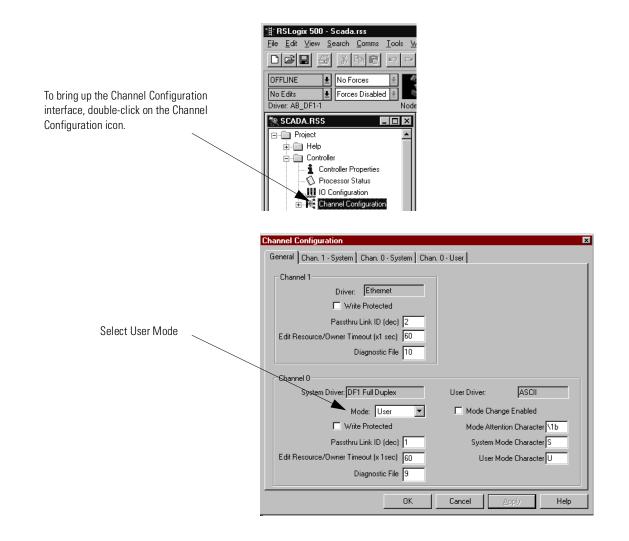

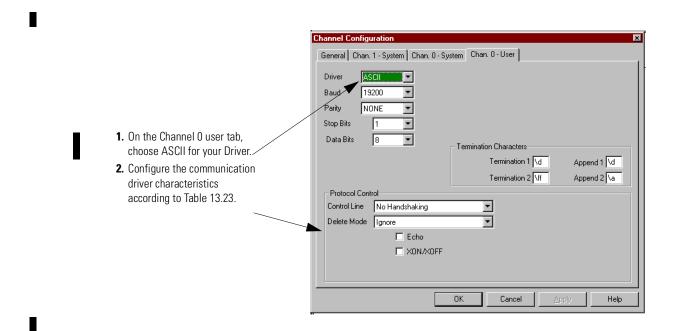

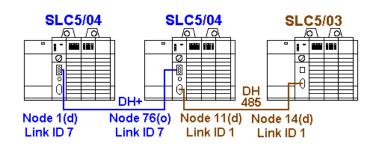

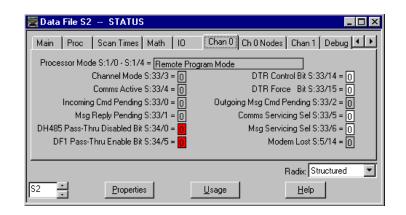

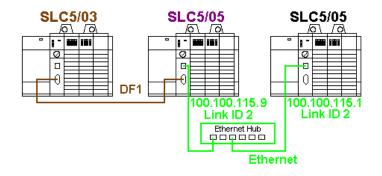

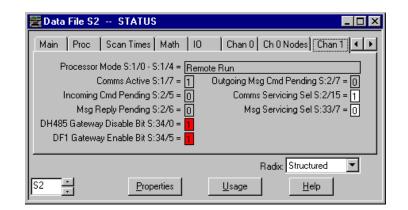

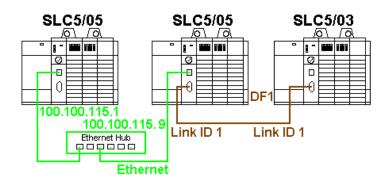

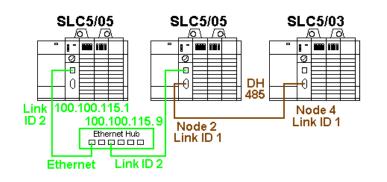

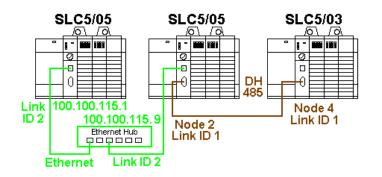

| SLC Communication Channels     | Overview13-1DH-485 Communications13-3Configuring a Channel for DH-48513-6Data Highway Plus Communications13-9Configuring Channel 1 for DH+13-11Ethernet Communications13-21Configuring Channel 1 for Ethernet13-23DF1 Communications13-37Configuring Channel 0 for DF1 Full-Duplex13-39Configuring Channel 0 for Standard-Mode13-43DF1 Half-Duplex Master13-43Configuring Channel 0 for DF1 Half-Duplex Slave13-51Configuring Channel 0 for DF1 Half-Duplex Slave13-54Configuring Channel 0 for DF1 Half-Duplex Slave13-57Using Modems that Support DF113-58Modem Control Line Operation in13-60RTS Send Delay and RTS Off Delay Parameters13-63Configuring Channel 0 for ASCII Communications13-64SLC 5/05 Embedded Web Server Capability13-66 |

|                                | Chapter 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

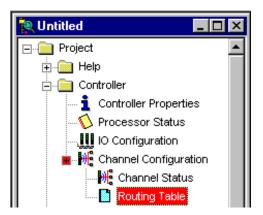

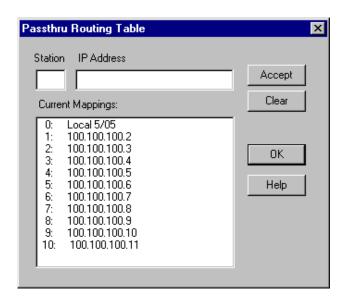

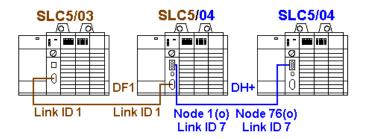

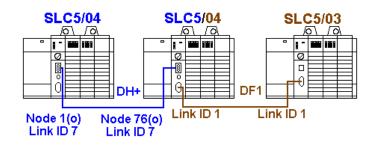

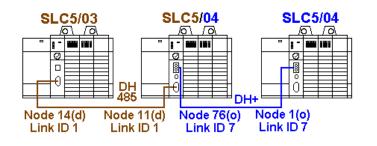

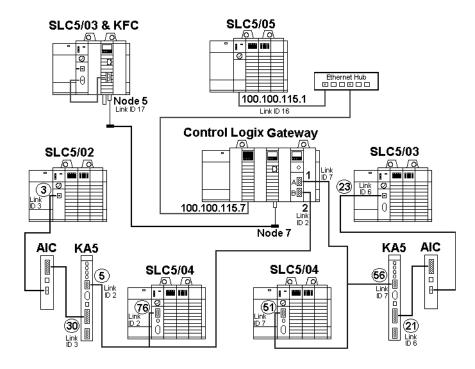

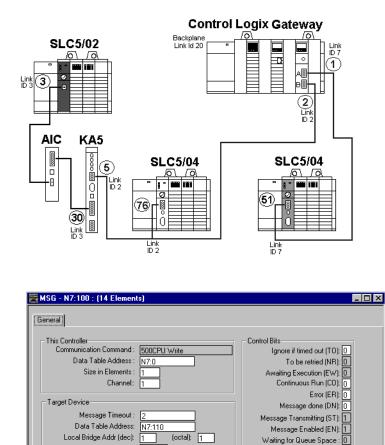

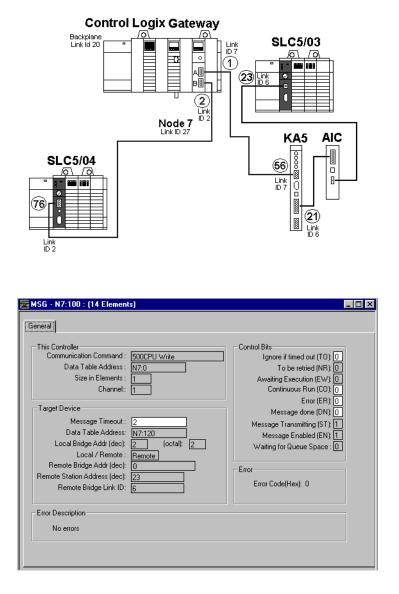

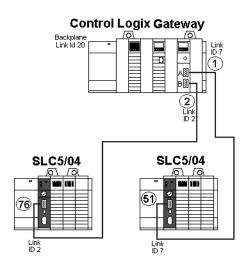

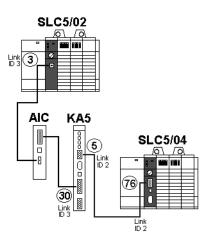

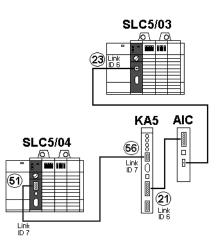

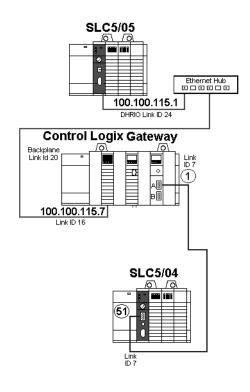

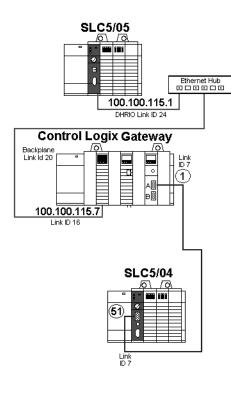

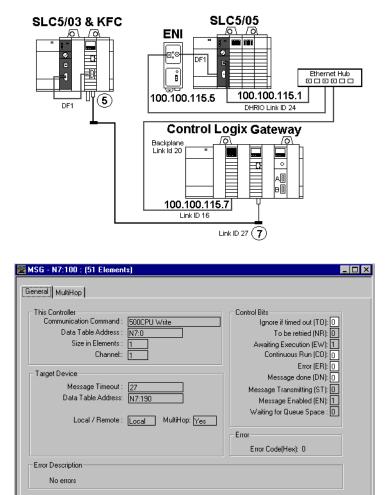

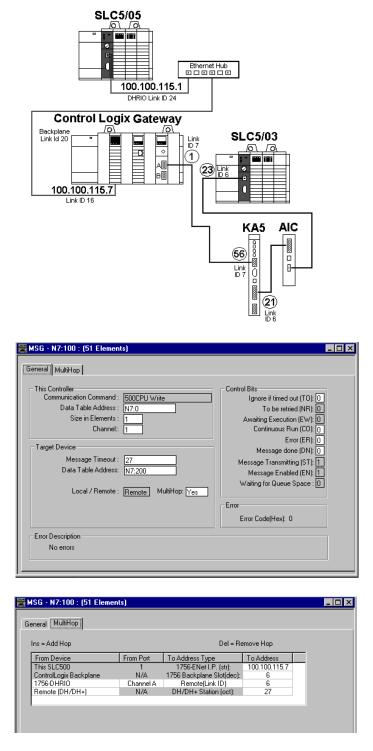

| Messaging Examples             | Local versus Remote type Message.14-1Remote Terminology.14-2Using the Passthru Features.14-3DF1 and DH485 (RS232 port CH0) to EthernetChannel-to-Channel Passthru(SLC 5/05 Processors OS501 FRN3 and above processors).14-9SLC 5/04 Passthru ExamplesSLC 5/05 Passthru Examples14-16Remote Examples14-23                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Chapter 12

**Troubleshooting Faults**

## SLC 5/03 (OS30x), SLC 5/04 (OS40x) and SLC 5/05 (OS50x) Firmware History

## Chapter 15

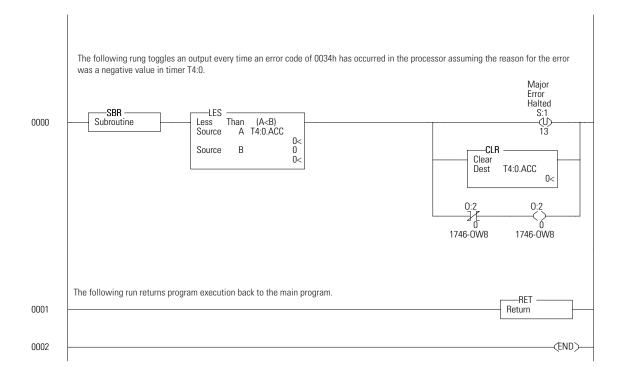

| Automatically Clearing Faults                        |

|------------------------------------------------------|

| Manually Clearing Faults                             |

| Troubleshooting SLC 5/03 and Higher Processors 15-14 |

## Appendix A

| ••                        |    |

|---------------------------|----|

| OS300, Series A, FRN 1    |    |

| released: June 1993 A     | -1 |

| OS300, Series A, FRN 2    |    |

| released: July 1993 A     | -1 |

| OS300, Series A, FRN 3    |    |

| released: March 1994 A    | -1 |

| OS300, Series A, FRN 4    |    |

| released: May 1994        | -1 |

| OS301, Series A, FRN 5    |    |

| released: August 1994     | -1 |

| OS400, Series A, FRN 1    |    |

| released: August 1994     | -2 |

| OS301, Series A, FRN 6    |    |

| OS400, Series A, FRN 2    |    |

| released: November 1994 A | -3 |

| OS301, Series A, FRN 7    |    |

| 0S400, Series A, FRN 3    |    |

| released: March 1995      | -3 |

| OS301, Series A, FRN 8    |    |

| OS400, Series A, FRN 4    |    |

| released: April 1995      | -4 |

| OS302, Series A, FRN 9    |    |

| OS401, Series A, FRN 5    |    |

| released: December 1995   | -4 |

| OS401, Series A, FRN 6    |    |

| released: May 1996        | -5 |

| OS302, Series B, FRN 10   |    |

| OS401, Series B, FRN 7    |    |

| released: July 1997 A     | -5 |

| OS500, Series A, FRN 1    |    |

| released: October 1997 A  | -6 |

| OS302, Series B, FRN 11   |    |

| OS401, Series B, FRN 8    |    |

| OS500, Series A, FRN 2    |    |

| released: November 1997 A | -6 |

|                           |    |

| OS302, Series B, FRN 12                          |                                       |

|--------------------------------------------------|---------------------------------------|

| released: November 1998                          |                                       |

| OS401, Series B, FRN 9                           |                                       |

| released: July, 1999                             |                                       |

| OS501, Series A, FRN 3                           |                                       |

| released: July 1998                              | A-6                                   |

| OS302, Series B, FRN 12                          |                                       |

| released: November 1998                          |                                       |

| OS401, Series B, FRN 9                           |                                       |

| released: July 1999                              |                                       |

| OS501, Series A, FRN 4                           |                                       |

| released: February 1999                          | A-6                                   |

| OS302, Series B, FRN 14                          |                                       |

| OS401, Series B, FRN 9                           |                                       |

| released: July 1999                              |                                       |

| OS501, Series A, FRN 4                           |                                       |

| released: February, 1999                         | A-6                                   |

| OS501, Series A, FRN 5                           |                                       |

|                                                  | A-7                                   |

| OS302, Series C, FRN 3                           |                                       |

| OS401, Series C, FRN 3                           |                                       |

| DS501, Series C, FRN 3                           |                                       |

| 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2          | A-7                                   |

| OS302, Series C, FRN 4                           | · · · · · · · · · · · · · · · · · · · |

| OS401, Series C, FRN 4                           |                                       |

| OS501, Series C, FRN 4                           |                                       |

| eleased: February 2001                           | A-12                                  |

| OS302, Series C, FRN 5                           | A-12                                  |

| OS401, Series C, FRN 5                           |                                       |

| , , ,                                            |                                       |

| OS501, Series C, FRN 5<br>released: October 2001 | A 10                                  |

| released: October 2001                           | A-12                                  |

| Annendiu D                                       |                                       |

| Appendix B                                       |                                       |

| Status File Overview                             |                                       |

| Status File Details                              | B-4                                   |

| Appendix C                                       |                                       |

| ••                                               | 0.1                                   |

| Memory Usage Overview                            |                                       |

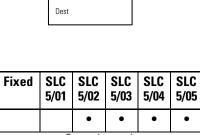

| Fixed and SLC 5/01 Processors                    |                                       |

| SLC $5/02$ Processor                             |                                       |

| User Word Comparison Between SLC 5/03            | e                                     |

| Processors and the SLC $5/02$ Processor          |                                       |

| SLC 5/03, SLC 5/04 and SLC 5/05 Processor        | r C-13                                |

|                                                  |                                       |

**SLC Status File**

Memory Usage

|                                              | Appendix D                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programming Instruction<br>References        | Valid Addressing Modes and File Types D-1                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                              | Appendix E                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Data File Organization and<br>Addressing     | Understanding File OrganizationE-1Addressing Data FilesE-3M0 and M1 Data Files - Specialty I/O ModulesE-19G Data Files - Specialty I/O ModulesE-25                                                                                                                                                                                                                                                                                           |

|                                              | Appendix F                                                                                                                                                                                                                                                                                                                                                                                                                                   |

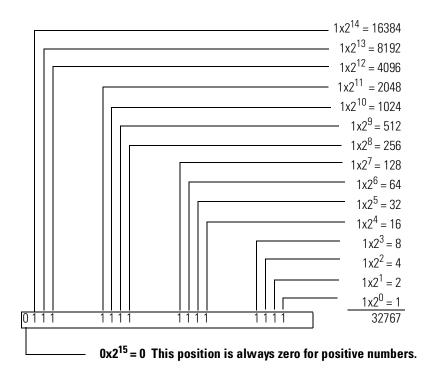

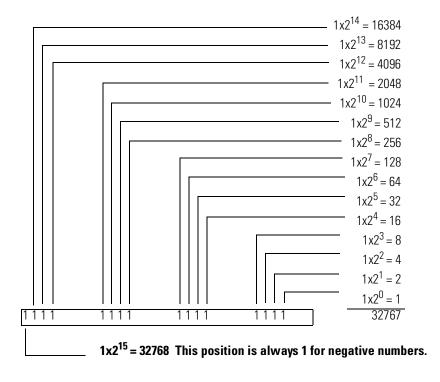

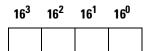

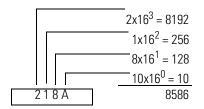

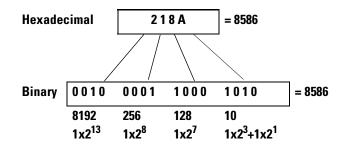

| Number Systems                               | Binary NumbersF-1Hexadecimal NumbersF-3Hex MaskF-5Binary Floating-Point ArithmeticF-6                                                                                                                                                                                                                                                                                                                                                        |

|                                              | Appendix G                                                                                                                                                                                                                                                                                                                                                                                                                                   |

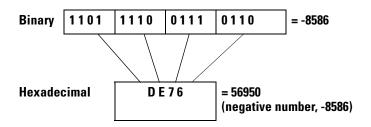

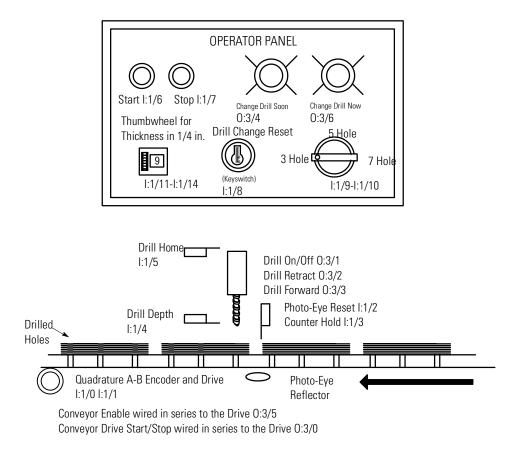

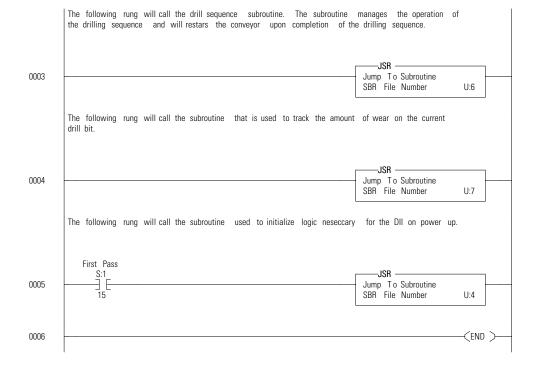

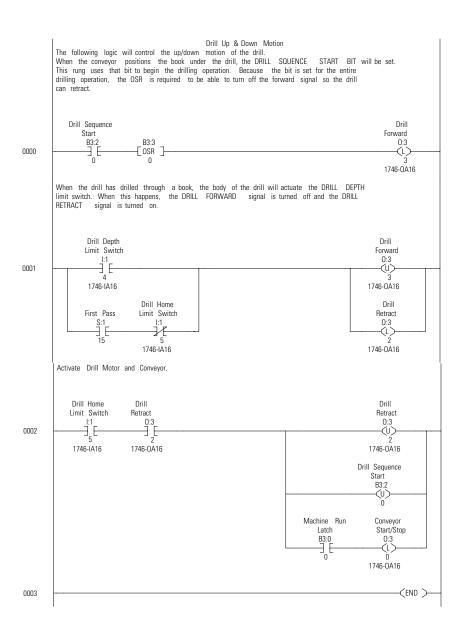

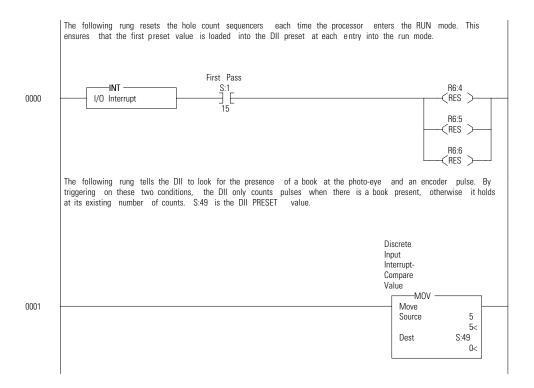

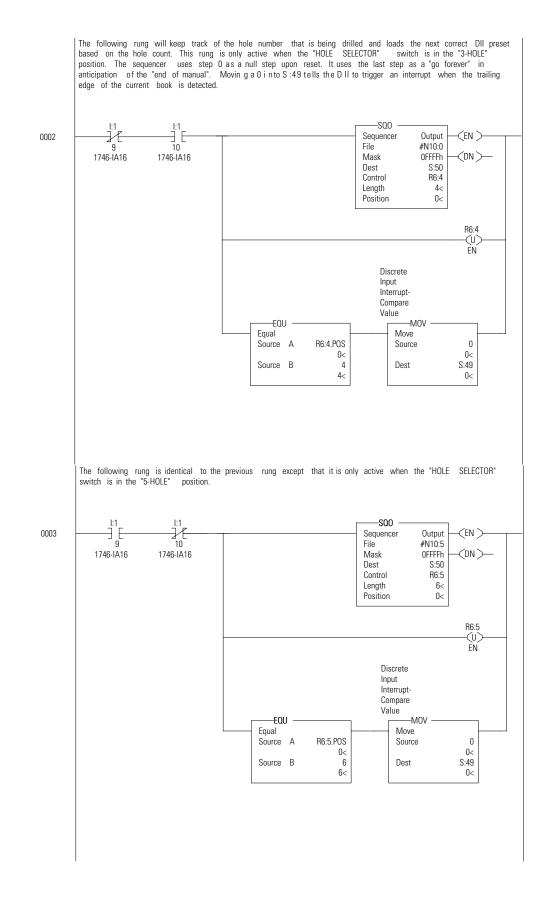

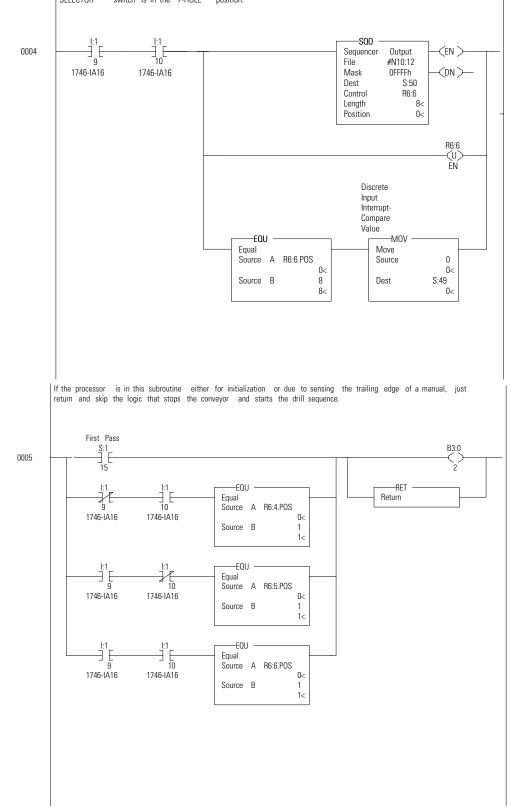

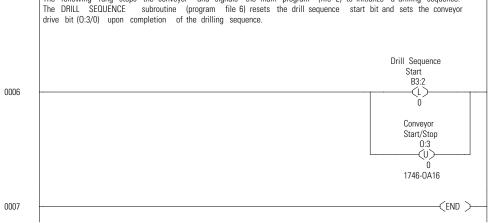

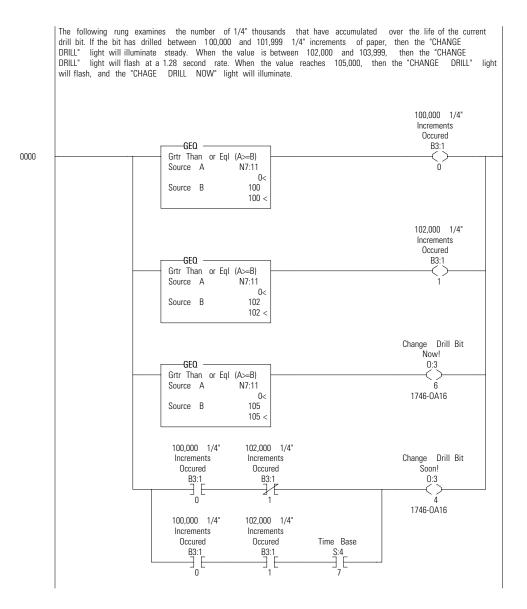

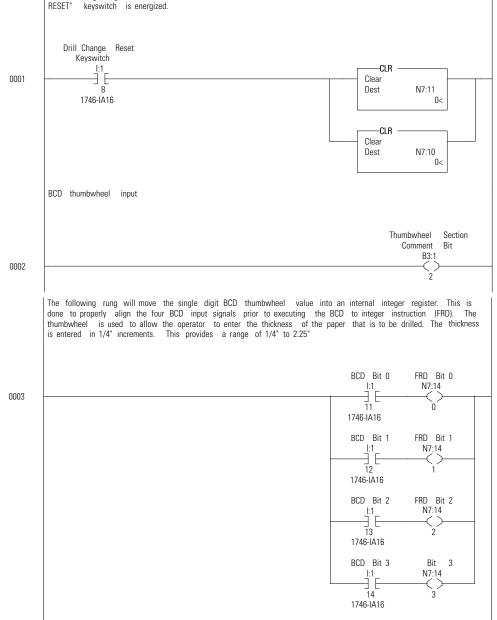

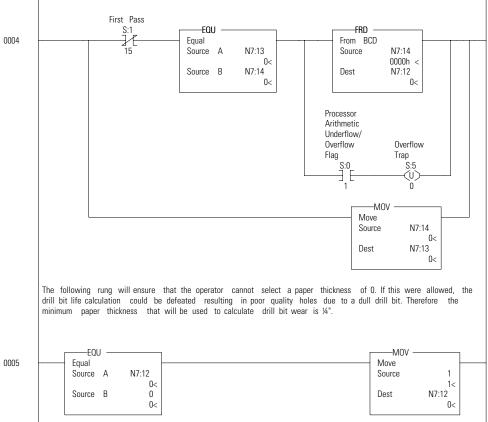

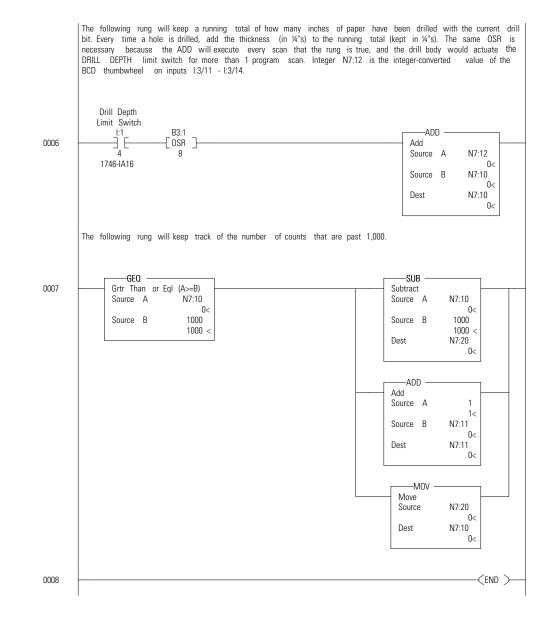

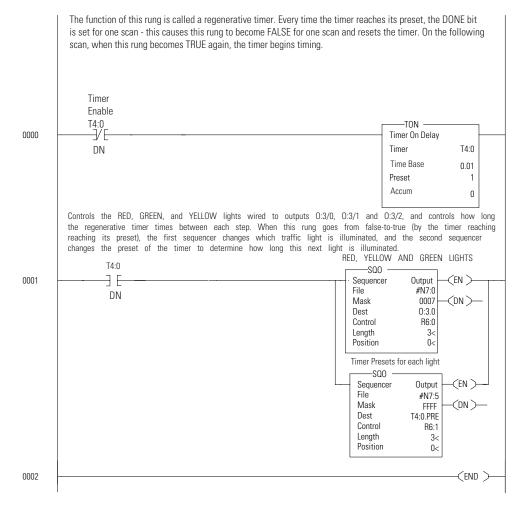

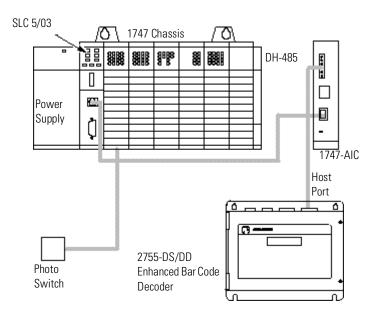

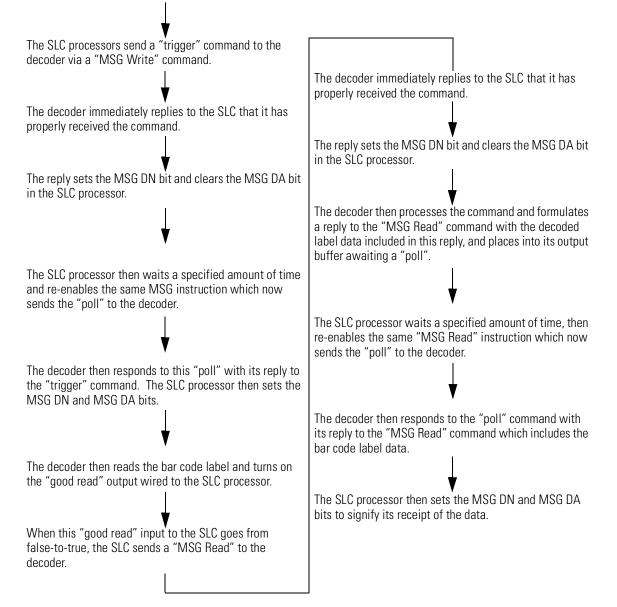

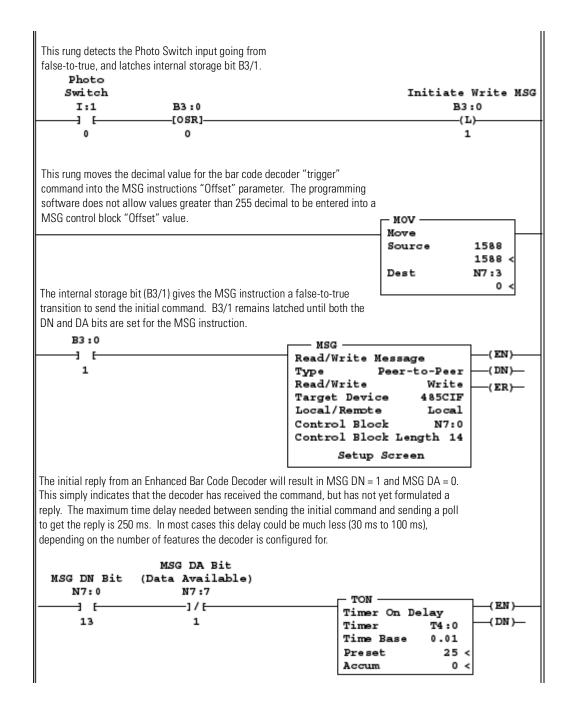

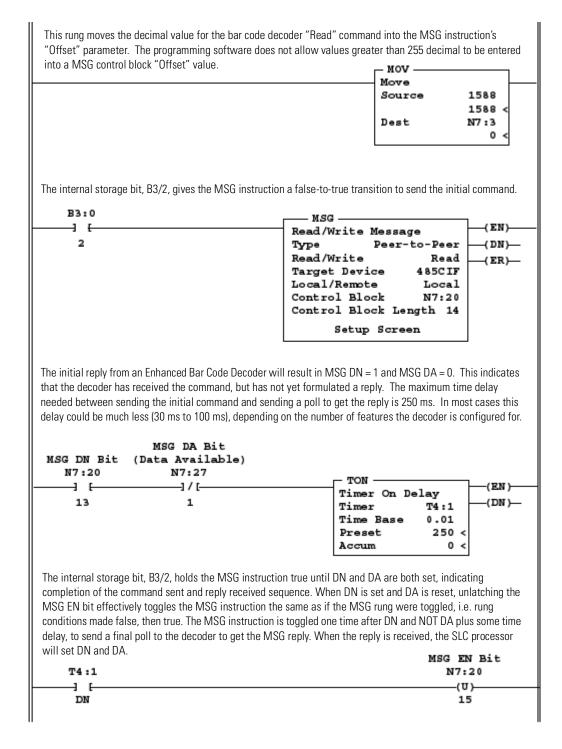

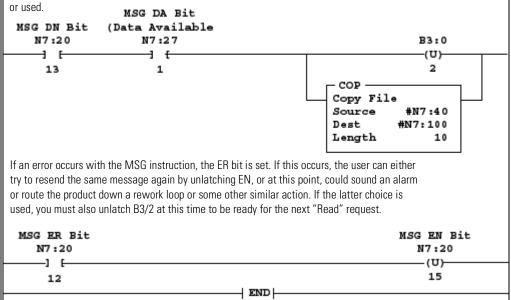

| Application Example Programs                 | Paper Drilling Machine Application ExampleG-1Paper Drilling Machine Operation OverviewG-3Time Driven Sequencer Application ExampleG-14Time Driven Sequencer Ladder ProgramG-14Event Driven Sequencer Application ExampleG-15Event Driven Sequencer Ladder ProgramG-15On/Off Circuit Application ExampleG-16On/Off Circuit Ladder ProgramG-17Interfacing with Enhanced Bar Code DecodersG-17Over DH-485 Network Using the MSG InstructionG-17 |

| Index                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SLC 500 Alphabetical List of<br>Instructions |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                          | Read this preface to familiarize yourself with the rest of the manual. It provides information concerning:                                                                                                                                                                                         |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | <ul> <li>who should use this manual</li> <li>the purpose of this manual</li> <li>related documentation</li> <li>conventions used in this manual</li> <li>Rockwell Automation support</li> </ul>                                                                                                    |

| Who Should Use this<br>Manual            | Use this manual if you are responsible for designing, installing, programming, or troubleshooting control systems that use SLC 500 processors.                                                                                                                                                     |

|                                          | You should have a basic understanding of electrical circuitry and familiarity with relay logic. If you do not, obtain the proper training before using this product.                                                                                                                               |

| Purpose of this Manual                   | <ul> <li>This manual is a reference guide for SLC 500 processors. This manual:</li> <li>provides status file functions</li> <li>provides the instructions used in your ladder logic programs</li> <li>compliments the online help available at the terminal</li> </ul>                             |

| Common Techniques Used<br>in this Manual | <ul> <li>The following conventions are used throughout this manual:</li> <li>Bulleted lists such as this one provide information, not procedural steps.</li> <li>Numbered lists provide sequential steps or hierarchical information.</li> <li><i>Italic</i> type is used for emphasis.</li> </ul> |

## Rockwell Automation Support

Rockwell Automation offers support services worldwide, with over 75 Sales/Support Offices, 512 authorized Distributors and 260 authorized Systems Integrators located throughout the United States alone, plus Rockwell Automation representatives in every major country in the world.

## **Local Product Support**

Contact your local Rockwell Automation representative for:

- sales and order support

- product technical training

- warranty support

- support service agreements

## **Technical Product Assistance**

If you need to contact Rockwell Automation for technical assistance, please review the *Troubleshooting* chapter on page 15-1 in this manual first. Then call your local Rockwell Automation representative.

## Your Questions or Comments on this Manual

If you find a problem with this manual, or you have any suggestions for how this manual could be made more useful to you, please contact us at the address below:

Rockwell Automation Automation Control and Information Group Technical Communication, Dept. A602V P.O. Box 2086 Milwaukee, WI 53201-2086

or visit our internet page at: <u>http://www.ab.com</u> or <u>http://www.rockwellautomation.com</u>

Read this preface to familiarize yourself with the rest of the manual. It provides information concerning:

- who should use this manual

- purpose of this manual

- conventions used in this manual

## **Related Documentation**

The following documents contain additional information concerning Allen-Bradley SLC products. To obtain a copy, contact your local Allen-Bradley office or distributor.

| For                                                                                     | Read this Document                                                                                                       |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| An overview of the SLC 500 family of products                                           | SLC 500 System Overview, Publication<br>Number 1747-S0001B-EN-P.                                                         |

| A description on how to install and use your<br>Fixed SLC 500 programmable controller   | Installation and Operation Manual for Fixed<br>Hardware Style Programmable Controllers,<br>Publication Number 1747-6.1   |

| A description on how to install and use your<br>Modular SLC 500 programmable controller | Installation and Operation Manual for<br>Modular Hardware Style Programmable<br>Controllers, Publication Number 1747-6.2 |

| A glossary of industrial automation terms and abbreviations                             | Allen-Bradley Industrial Automation Glossary,<br>Publication Number AG-7.1                                               |

## **Processor Files**

## **File Structure**

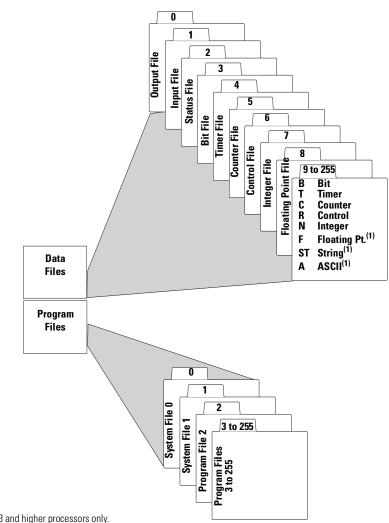

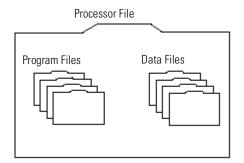

SLC 500 user memory is comprised of Data Files and Program Files.

The file types shown below for data files 3 through 8 are the default values. Files 9 to 255 can be configured to be bit, timer, counter, control, integer, floating point, ASCII, or String files.

(1) SLC 5/03 and higher processors only.

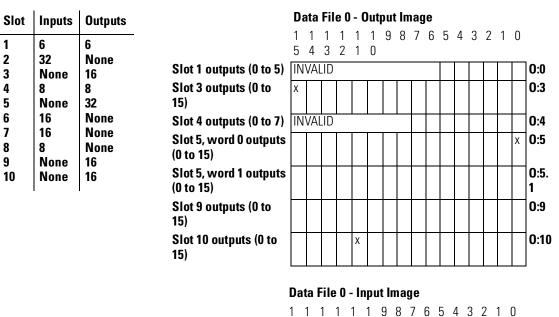

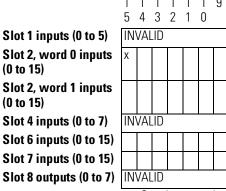

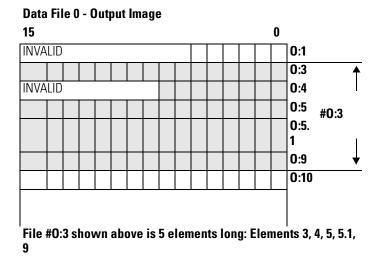

## Output and Input Data Files (Files 00: and I1:)

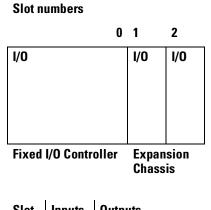

Data Files 0 and 1 represent external outputs and inputs, respectively. Bits in file 1 are used to represent external inputs. In most cases, a single 16-bit word in these files will correspond to a slot location in your controller, with bit numbers corresponding to input or output terminal numbers. Unused bits of the word are not available for use.

Table 1.1 explains the addressing format for outputs and inputs. Note that the format specifies  $\mathbf{e}$  as the slot number and  $\mathbf{s}$  as the word number. When referencing output and input data file words, refer to the element as  $\mathbf{e.s}$  (slot and word), taken together.

Table 1.1 Output and Input Data File Addressing Formats

| Format                                         | Explanat                                                          | Explanation                                   |                                                                                                                                                                       |  |  |  |  |  |  |  |

|------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| O:e.s/b                                        | 0                                                                 | Output                                        |                                                                                                                                                                       |  |  |  |  |  |  |  |

| l:e.s/b                                        | I                                                                 | Input                                         | Input                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                | :                                                                 | Element delimiter                             | Element delimiter                                                                                                                                                     |  |  |  |  |  |  |  |

|                                                | e                                                                 | Slot number (decimal)                         | Slot 0, adjacent to the power supply in the first chassis, applies to the processor module (CPU). Succeeding slots are I/O slots, numbered from 1 to a maximum of 30. |  |  |  |  |  |  |  |

|                                                | •                                                                 | Word delimiter.                               | Required only if a word number is necessary as noted below.                                                                                                           |  |  |  |  |  |  |  |

|                                                | S                                                                 | Word number                                   | Required if the number of inputs or outputs exceeds 16 for the slot.<br>Range: 0-255 (range accommodates multi-word "specialty cards")                                |  |  |  |  |  |  |  |

|                                                | 1                                                                 | Bit delimiter                                 |                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                                | b                                                                 | Terminal number                               | Inputs: 0-15<br>Outputs: 0-15                                                                                                                                         |  |  |  |  |  |  |  |

| Examples:                                      |                                                                   |                                               |                                                                                                                                                                       |  |  |  |  |  |  |  |

| 0:3/15<br>0:5/0<br>0:10/11<br>1:7/8<br>1:2.1/3 | Output 15<br>Output 0,<br>Output 11<br>Input 8, sl<br>Input 3, sl | slot 5<br>, slot 10                           |                                                                                                                                                                       |  |  |  |  |  |  |  |

| 0:5<br>0:5.1<br>I:8                            |                                                                   | ord 0, slot 5<br>ord 1, slot 5<br>d 0, slot 8 |                                                                                                                                                                       |  |  |  |  |  |  |  |

Default Values: Your programming device will display an address more formally. For example, when you assign the address 0:5/0, the programming device will show it as 0:5.0/0 (Output file, slot 5, word 0, terminal 0).

## Status File (File S2:)

You cannot add to or delete from the status file. See Table 1.2 to understand how to address various bits and words within the status file. You can address various bits and words as follows:

| Format    | Explanation   | 1                                                                                                              |                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|-----------|---------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| S:e/b     | S             | Status file                                                                                                    | Status file                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|           | :             | Element delimiter                                                                                              |                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|           | e             | Element number                                                                                                 | Ranges from 0 to 15 in a fixed or SLC 5/01 controller,<br>0 to 32 in an SLC 5/02,<br>0 to 82 in an SLC 5/03 and<br>0 to 82 in an SLC 5/05,<br>0 to 96 in an SLC 5/04 OS400, and<br>0 to 163 in an SLC 5/04 OS401 processors.<br>These are 1-word elements. 16 bits per element. |  |  |  |  |  |  |  |

|           | 1             | Bit delimiter                                                                                                  | Bit delimiter                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|           | b             | Bit number                                                                                                     | Bit location within the element. Ranges from 0 to 15.                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Examples: |               |                                                                                                                |                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| S:1/15    | Element 1, bi | Element 1, bit 15. This is the "first pass" bit, which you can use to initialize instructions in your program. |                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| S:3       | Element 3. Tl | he lower byte of this element                                                                                  | is the current scan time. The upper byte is the watchdog scan time.                                                                                                                                                                                                             |  |  |  |  |  |  |  |

#### **Table 1.2 Status File Addressing Format**

## Bit Data File (B3:)

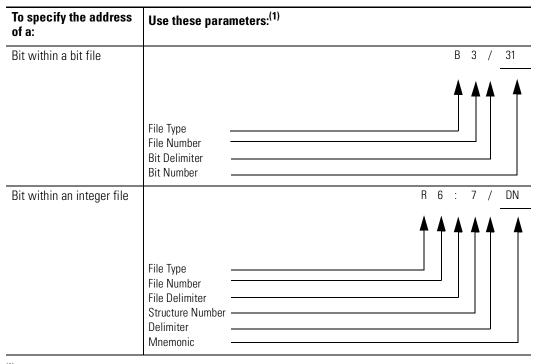

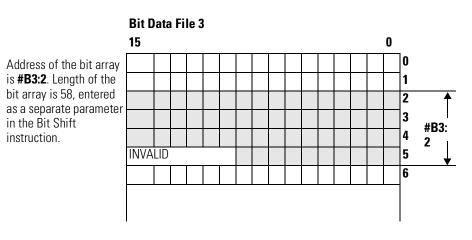

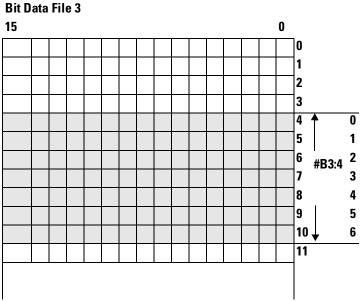

File 3 is the bit file, used primarily for bit (relay logic) instructions, shift registers, and sequencers. The maximum size of the file is 256 1-word elements, a total of 4096 bits. You can address bits by specifying the element number (0 to 255) and the bit number (0 to 15) within the element. You can also address bits by numbering them in sequence, 0 to 4095.

You can also address elements of this file. See Table 1.3 for a detailed format description. Note the two different possible formats that can be used.

**Table 1.3 Bit File Addressing Format**

| Format    | Explanation        |                                                    |                                                                                                                       |  |  |  |  |  |  |

|-----------|--------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bf:e/b    | В                  | B Bit type file                                    |                                                                                                                       |  |  |  |  |  |  |

|           | f                  |                                                    | File number. Number 3 is the default file. A file number between 9-255 can be used if additional storage is required. |  |  |  |  |  |  |

|           | :                  | Element delimiter                                  |                                                                                                                       |  |  |  |  |  |  |

|           | e                  | Element number                                     | Ranges from 0-255. These are 1-word elements. 16 bits per element.                                                    |  |  |  |  |  |  |

|           | 1                  | Bit delimiter                                      |                                                                                                                       |  |  |  |  |  |  |

|           | b                  | Bit number                                         | Bit location within the element. Ranges from 0-15.                                                                    |  |  |  |  |  |  |

| Bf/b      | B<br>f<br>/        | Same as above.<br>Same as above.<br>Same as above. | Same as above.                                                                                                        |  |  |  |  |  |  |

|           | b                  | Bit number                                         | Numerical position of the bit within the file. Ranges from 0-4095.                                                    |  |  |  |  |  |  |

| Examples: |                    |                                                    |                                                                                                                       |  |  |  |  |  |  |

| B3:3/14   | Bit 14, element 3  |                                                    |                                                                                                                       |  |  |  |  |  |  |

| B3:252/00 | Bit 0, element 252 | Bit 0, element 252                                 |                                                                                                                       |  |  |  |  |  |  |

| B3:9      | Bit 62             | Bit 62                                             |                                                                                                                       |  |  |  |  |  |  |

| B3/62     | Bit 62             |                                                    |                                                                                                                       |  |  |  |  |  |  |

| B3/4032   | Bit 4032           |                                                    |                                                                                                                       |  |  |  |  |  |  |

## **Timer Data File (T4:)**

Timing could be inaccurate if Jump (JMP), Label (LBL), Jump to Subroutine (JSR), or Subroutine (SBR) instructions skip over the rung containing a timer instruction while the timer is timing. If the skip duration is less than 2.5 seconds, no time will be lost; if the skip duration exceeds 2.5 seconds, an undetectable timing error occurs. When using subroutines, a timer must be executed at least every 2.5 seconds to prevent a timing error.

Timer instructions use various control bits. These are 3-word elements, used with Bit, TON, TOF and RTO instructions. Word 0 is the status word, word 1 indicates the preset value, and word 2 indicates accumulator value. This is shown in Table 1.4.

#### **Table 1.4 Timer Control Fields**

| 15     | 14                      | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6                           | 5 | 4 | 3 | 2 | 1 | 0 | Word |

|--------|-------------------------|----|----|----|----|---|---|---|-----------------------------|---|---|---|---|---|---|------|

| EN     | TT                      | DN |    |    |    |   |   |   | Internal Use <sup>(1)</sup> |   |   |   |   |   | 0 |      |

| Preset | Preset Value (PRE)      |    |    |    |    |   |   |   |                             | 1 |   |   |   |   |   |      |

| Accum  | Accumulator Value (ACC) |    |    |    |    |   |   |   |                             | 2 |   |   |   |   |   |      |

(1) Bits labeled "Internal Use" are not addressable.

| Addressable Bits           | Addressable Words       |

|----------------------------|-------------------------|

| EN = Enable (Bit 15)       | PRE = Preset Value      |

| TT = Timer Timing (Bit 14) | ACC = Accumulated Value |

| DN = Done (Bit 13)         |                         |

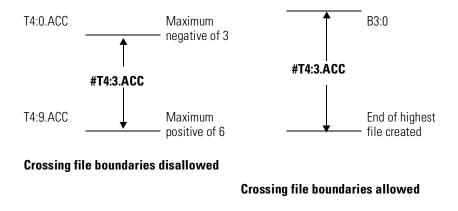

## **Addressing Structure**

Address bits and words using the format Tf:e.s/b

#### **Table 1.5 Timer Addressing Format**

| Explanation            |                                                                                                                          |                                                      |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|

| Т                      | Timer file                                                                                                               |                                                      |  |  |  |  |

| f                      | File number. For SLC 500 processors the default is 4. A file number between 9 to 255 can be used for additional storage. |                                                      |  |  |  |  |

| :                      | Element delimiter                                                                                                        |                                                      |  |  |  |  |

| е                      | Element number                                                                                                           | These are 3-word elements.<br>The range is 0 to 255. |  |  |  |  |

|                        | Word Delimiter                                                                                                           | Range 0 to 2                                         |  |  |  |  |

| S                      | Word Number                                                                                                              |                                                      |  |  |  |  |

| 1                      | Bit delimiter                                                                                                            |                                                      |  |  |  |  |

| b                      | Bit Number Range 0 to 15                                                                                                 |                                                      |  |  |  |  |

| Examples               |                                                                                                                          |                                                      |  |  |  |  |

| T4:0/15 or T4:0/EN     | Enable bit                                                                                                               |                                                      |  |  |  |  |

| T4:0/14 or T4:0/TT     | Timer timing bit                                                                                                         |                                                      |  |  |  |  |

| T4:0/13 or T4:0/DN     | Done bit                                                                                                                 |                                                      |  |  |  |  |

| T4:0.1 or T4:0.PRE     | Preset value of the timer                                                                                                |                                                      |  |  |  |  |

| T4:0.2 or T4:0.ACC     | Accumulated value of the timer                                                                                           |                                                      |  |  |  |  |

| T4:0.1/0 or T4:0.PRE/0 | Bit 0 of the preset value                                                                                                |                                                      |  |  |  |  |

| T4:0.2/0 or T4:0.ACC/0 | Bit 0 of the accumulated valu                                                                                            | IC                                                   |  |  |  |  |

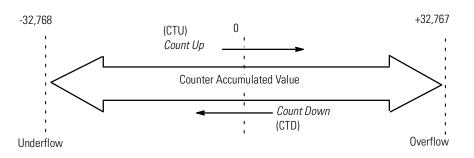

## **Counter Data File Elements (C5:)**

Each Counter address is made of a 3-word data file element. Word 0 is the control word, containing the status bits of the instruction. Word 1 is the preset value. Word 2 is the accumulated value.

The control word for counter instructions includes five status bits, as indicated below.

#### **Table 1.6 Counter Control Fields**

| 15     | 14                      | 13 | 12 | 11 | 10                | 09 | 08 | 07 | 06      | 05                    | 04 | 03 | 02 | 01 | 00 | Word |

|--------|-------------------------|----|----|----|-------------------|----|----|----|---------|-----------------------|----|----|----|----|----|------|

| CU     | CD                      | DN | 0V | UN | UA <sup>(1)</sup> |    |    |    | Interna | al Use <sup>(2)</sup> |    |    |    |    |    | 0    |

| Preset | Preset Value (PRE)      |    |    |    |                   |    |    |    | 1       |                       |    |    |    |    |    |      |

| Accum  | Accumulator Value (ACC) |    |    |    |                   |    |    |    | 2       |                       |    |    |    |    |    |      |

(1) Fixed SLC 500 only.

(2) Bits labeled "Internal Use" are not addressable.

| Addressable Bits                                                | Addressable Words |

|-----------------------------------------------------------------|-------------------|

| CU = Count up enable (Bit 15)                                   | PRE = Preset      |

| CD = Count down enable (Bit 14)                                 | ACC = Accum       |

| DN = Done bit (Bit 13)                                          |                   |

| OV = Overflow bit (Bit 12)                                      |                   |

| UN = Underflow bit (Bit 11)                                     |                   |

| UA = Update Accumulator bit (Bit 10) (Fixed<br>Controller Only) |                   |

### **Entering Parameters**

There are several parameters associated with Counter instructions. The following parameters detail the operations of the counter.

#### Accumulator Value (ACC)

This is the number of false-to-true transitions that have occurred since the counter was last reset.

#### Preset Value (PRE)

Specifies the value which the counter must reach before the controller sets the done bit (DN). When the accumulator value becomes equal to or greater than the preset value, the done status bit is set. You can use the done bit (DN) to control an output device.

Preset and accumulated values for counters range from -32,768 to +32,767, and are stored as signed integers. Negative values are stored in two's complement form.

## **Addressing Structure**

Assign counter addresses using the format Cf:e.s/b

| Explanation        |                                                                                                                          |                                                      |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|

| C                  | Counter                                                                                                                  |                                                      |  |  |  |

| f                  | File number. For SLC 500 processors the default is 5. A file number between 9 to 255 can be used for additional storage. |                                                      |  |  |  |

| :                  | Element delimiter                                                                                                        |                                                      |  |  |  |

| e                  | Element number                                                                                                           | These are 3-word elements.<br>The range is 0 to 255. |  |  |  |

|                    | Word Delimiter                                                                                                           |                                                      |  |  |  |

| S                  | Word Element                                                                                                             | 0 to 2                                               |  |  |  |

| 1                  | Bit delimiter                                                                                                            |                                                      |  |  |  |

| b                  | Bit Number                                                                                                               | 0 to 15                                              |  |  |  |

| Examples           | ·                                                                                                                        |                                                      |  |  |  |

| C5:0/15 or C5:0/CU | Count up enable bit                                                                                                      |                                                      |  |  |  |

| C5:0/14 or C5:0/CD | Count down enable bit                                                                                                    |                                                      |  |  |  |

| C5:0/13 or C5:0/DN | Done bit                                                                                                                 |                                                      |  |  |  |

| C5:0/12 or C5:0/OV | Overflow bit                                                                                                             |                                                      |  |  |  |

|                    | -                                                                                                                        |                                                      |  |  |  |

#### Table 1.7 Counter File Addressing Format

| Explanation               |                                                           |

|---------------------------|-----------------------------------------------------------|

| C5:0/11 or C5:0/UN        | Underflow bit                                             |

| C5:0/10 or C5:0/UA        | Update accum. bit (use with HSC in fixed controller only) |

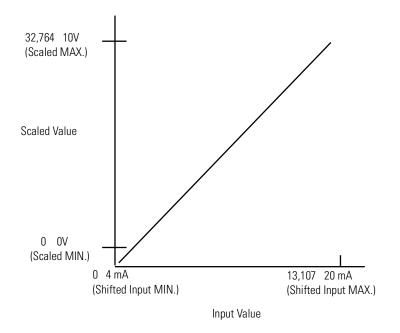

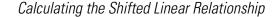

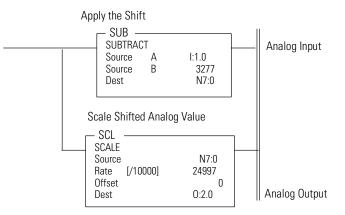

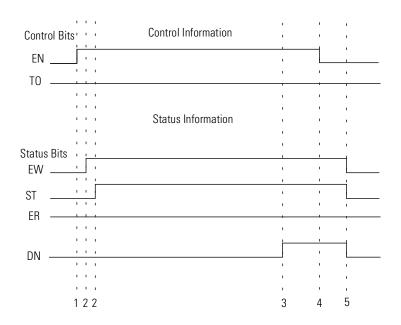

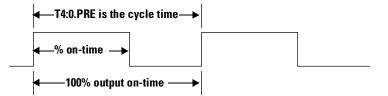

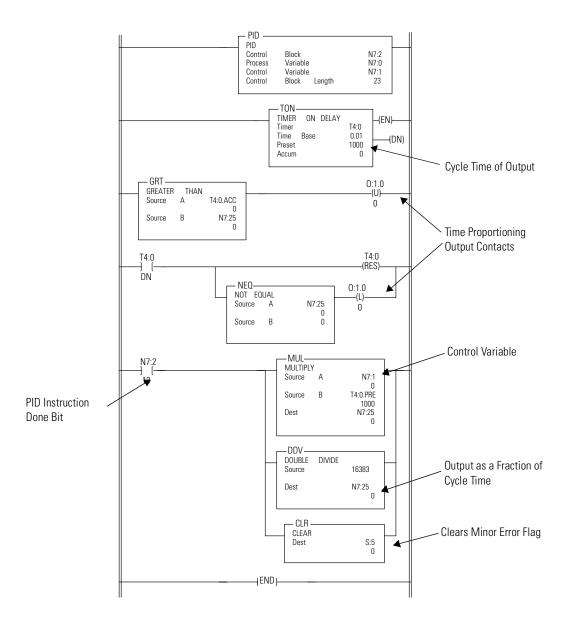

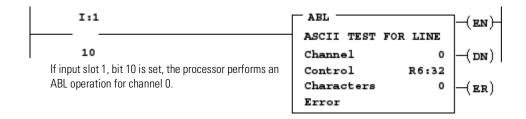

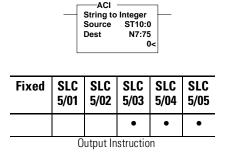

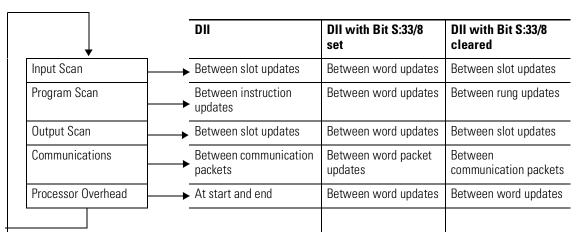

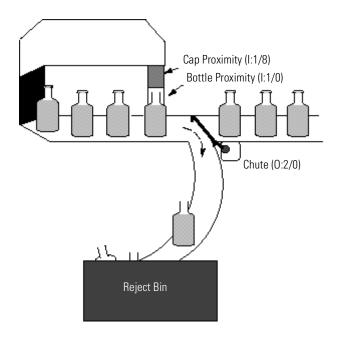

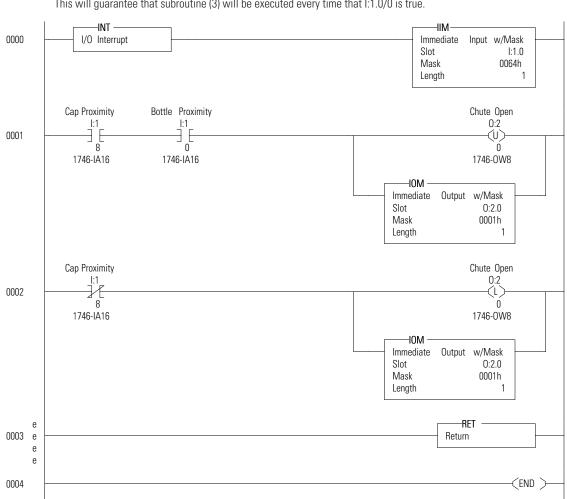

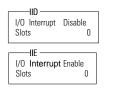

| C5:0.1 or C5:0.PRE        | Preset value of the counter                               |